# signetics

# FULLY DECODED RANDOM ACCESS 1024-BIT 1103-1 DYNAMIC MEMORY (HIGH SPEED VERSION)

# SILICON GATE MOS

#### DESCRIPTION

The Signetics 1103-1 is designed for main memory applications where high performance, low cost and large bit storage are important design objectives. It is a 1024 word by 1 bit random access memory element using enhancement mode P-channel MOS devices integrated on a monolithic array. It is fully decoded, permitting the use of an 18-pin dual in-line package. The dynamic circuitry dissipates significant power only during precharge. Information stored in the memory is nondestructively read. Refreshing of all 1024 bits is accomplished in 32 read cycles and is required every two milliseconds. A separate cenable (chip enable) lead allows easy selection of an individual package when outputs are OR-tied. Use Signetics 8T28 Sense Amp, and 3207 Clock Driver.

#### **FEATURES**

- LOW POWER DISSIPATION DISSIPATES POWER PRIMARILY ON SELECTED CHIPS

- ACCESS TIME 150 nsec.

- CYCLE TIME 340 nsec.

- REFRESH PERIOD 1 MILLISECOND FOR 0-55°C AMBIENT

- OR-TIE CAPABILITY

- SIMPLE MEMORY EXPANSION WITH CHIP ENABLE

- FULLY DECODED ON-CHIP ADDRESS DECODE

- INPUTS PROTECTED ALL INPUTS HAVE PRO-TECTION AGAINST STATIC CHARGE

- LOW COST PACKAGING 18 PIN SILICONE AND 18 PIN CERAMIC DUAL IN-LINE

#### APPLICATIONS

CORE MEMORY REPLACEMENT BUFFER STORES MAIN MEMORY

#### PROCESS TECHNOLOGY

The use of Signetics' unique silicon gate low threshold process allows the design and production of higher performance MOS circuits and provides higher functional density on a chip than other MOS technologies.

#### SILICONE PACKAGING

Low cost silicone DIP packaging is implemented and reliability is assured by the use of Signetics unique silicon gate MOS process technology. Unlike the standard metal gate MOS process, the silicon material over the gate oxide passivates the MOS transistors, and the deposited dielectric

#### SILICONE PACKAGING (Cont'd)

material over the silicon gate-oxide substrate structure provides an ion barrier. In addition, Signetics proprietary surface passivation and silicone packaging techniques result in an MOS circuit with inherent high reliability and demonstrating superior moisture resistance, mechanical shock and ionic contamination barriers.

#### PIN CONFIGURATION (Top View)

#### PART IDENTIFICATION TABLE

| ТҮРЕ     | PACKAGE             | OP. TEMP RANGE |

|----------|---------------------|----------------|

| 1103-1XA | 18-Pin DIP Silicone | 0–55°C         |

| 1103-11K | 18-Pin DIP Ceramic  | 0-55°C         |

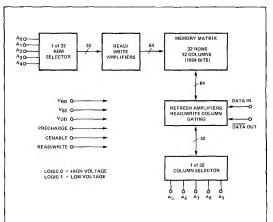

#### **BLOCK DIAGRAM**

#### **MAXIMUM GUARANTEED RATINGS (8)**

| Operating Ambient Temperature            | 0°C to 55°C     | Supply Voltages V <sub>DD</sub> and V <sub>SS</sub> |              |

|------------------------------------------|-----------------|-----------------------------------------------------|--------------|

| Storage Temperature                      | -65°C to +150°C | with Respect to VBB                                 | -25V to 0.3V |

| All Input or Output Voltages             |                 | Power Dissipation                                   | 1.0W         |

| with Respect to the Most                 |                 |                                                     |              |

| Positive Supply Voltage, V <sub>BB</sub> | -25V to 0.3V    |                                                     |              |

#### D.C. AND OPERATING CHARACTERISTICS

$T_A = 0^{\circ}C$  to  $-55^{\circ}C$ ,  $V_{SS}^{(1)} = 19V \pm 5\%$ ,  $(V_{BB} - V_{SS})^{(6)} = 3V$  to 4V,  $V_{DD} = 0V$  unless otherwise specified (Note 7).

| SYMBOL                          | TEST                                  | MIN.                | TYP.       | MAX.                | UNIT | CONDITIONS                                        |

|---------------------------------|---------------------------------------|---------------------|------------|---------------------|------|---------------------------------------------------|

| 1LI                             | Input Load Current (All input pins)   |                     |            | 10                  | μΑ   | V <sub>IN</sub> = 0V, T <sub>A</sub> = 25°C       |

| LO                              | Output Leakage Current                |                     |            | 10                  | μA   | V <sub>OUT</sub> = 0V, T <sub>A</sub> = 25°C      |

| IBB                             | VBB Supply Current                    |                     |            | 100                 | μA   |                                                   |

| 1DD1 <sup>(2)</sup>             | Supply Current During tPC             |                     | 45         | 60                  | mA   | All Addresses = 0V                                |

|                                 |                                       |                     |            |                     | 1    | Precharge = 0V                                    |

|                                 |                                       |                     |            |                     |      | Cenable = $V_{SS}$ ; $T_A = 25^{\circ}C$          |

| <sup>1</sup> DD2 <sup>(2)</sup> | Supply Current During t <sub>OV</sub> |                     | 50         | 68.5                | mA   | All addresses = 0V                                |

|                                 |                                       |                     |            | {                   |      | Precharge = 0V                                    |

|                                 |                                       |                     |            |                     |      | Cenable = $0V$ ; $T_A = 25^{\circ}C$              |

| 1DD3 <sup>(2)</sup>             | Supply Current During tPOV            | - ·· -              | 8.5        | 11                  | mΑ   | Precharge = V <sub>SS</sub>                       |

|                                 |                                       |                     |            |                     |      | Cenable = 0V; T <sub>A</sub> = 25°C               |

| <sup>1</sup> DD4 <sup>(2)</sup> | Supply Current During tCP             |                     | 3          | 4                   | mA   | Precharge = V <sub>SS</sub>                       |

|                                 |                                       |                     |            |                     |      | Cenable = V <sub>SS</sub> ; T <sub>A</sub> = 25°C |

| IDD <sup>(5)AV</sup>            | Average Supply Current                |                     | 20         | 23                  | mA   | Precharge Width = 150ns @ 50%                     |

|                                 |                                       |                     |            |                     |      | Cycle Time ≈ 340 ns; T <sub>A</sub> = 25°C        |

| VIL1                            | Input Low Voltage (All address        | V <sub>SS</sub> -20 |            | V <sub>SS</sub> -18 | v    |                                                   |

|                                 | and data-in lines)                    |                     |            |                     |      |                                                   |

| VIH1                            | Input High Voltage (All Inputs)       | V <sub>SS</sub> -1  |            | V <sub>SS</sub> +1  | v    |                                                   |

| IOH1                            | Output High Current                   | 1.15                | 1.3        | 7.0                 | mA   | T <sub>A</sub> = 25°C <b>1</b>                    |

| IOH2                            | Output High Current                   | 0.9                 | 1.15       | 7.0                 | mA   | T <sub>A</sub> ≈ 55°C                             |

| <sup>I</sup> OL                 | Output Low Current                    |                     | See Note 3 |                     | 1    | • R <sub>LOAD</sub> = 100Ω <sup>(4)</sup>         |

| VOH1                            | Output High Voltage                   | 115                 | 130        | 700                 | mV   | T <sub>A</sub> = 25°C                             |

| V <sub>OH2</sub>                | Output High Voltage                   | 90                  | 115        | 700                 | mV   | T <sub>A</sub> = 55°C                             |

| VOL                             | Output Low Voltage                    |                     | See Note 3 |                     | 0    | 1                                                 |

#### NOTES:

- 1. The V<sub>SS</sub> current drain is equal to  $(I_{DD} + I_{OH})$  or  $(I_{DD} + I_{OL})$ .

- 2. See Supply Current vs. Temperature (p. 3) for guaranteed current at the temperature extremes. These values are taken from a single pulse measurement.

- The output current when reading a low output is the leakage current of the 1103-1 plus external noise coupled into the output line from the clocks. V<sub>OL</sub> equals I<sub>OL</sub> across the load resistor.

- 4. This value of load resistance is used for measurement purposes. In applications the resistance may range from 100Ω to 1 kΩ.

- 5. This parameter is periodically sampled and is not 100% tested.

- (V<sub>BB</sub> V<sub>SS</sub>) supply should be applied at or before V<sub>SS</sub>.

- 7. Manufacturer reserves the right to make design and process changes and improvements.

- 8. Stresses above those listed under "Maximum Guaranteed Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

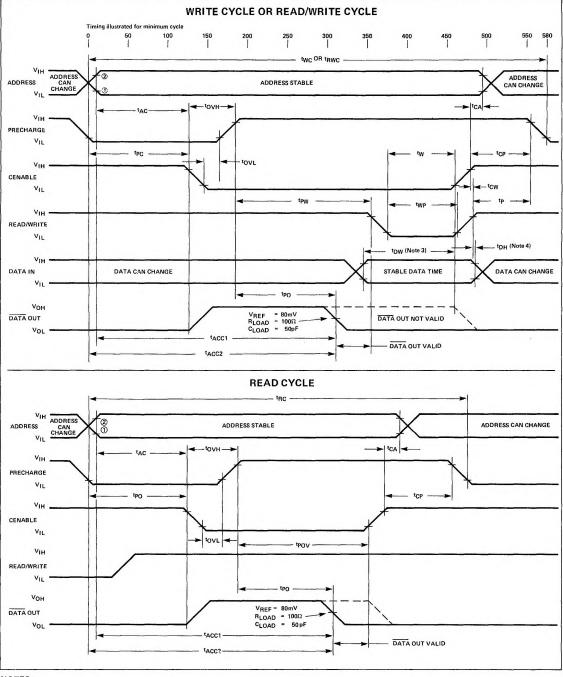

### AC CHARACTERISTICS $T_A = 0^{\circ}C$ to $+55^{\circ}C$ ; $V_{SS} = 19 \pm 5\%$ , $(V_{BB} - V_{SS}) = 3.0V$ to 4.0V, $V_{DD} = 0V$ READ, WRITE, AND READ/WRITE CYCLE

| SYMBOL           | TEST                              | MIN. | TYP. | MAX. | UNIT | CONDITIONS |

|------------------|-----------------------------------|------|------|------|------|------------|

| REF              | Time Between Refresh              |      |      | 1    | ms   |            |

| <sup>t</sup> AC  | Address to Cenable Set Up Time    | 30   |      |      | ns   |            |

| <sup>t</sup> CA  | Cenable to Address Hold Time      | 10   |      |      | ns   |            |

| <sup>t</sup> PC  | Precharge to Cenable Delay        | 60   |      |      | ns   |            |

| tovl             | Precharge & Cenable Overlap, Low  | 5    |      | 30   | ns   |            |

| <sup>t</sup> CP  | Cenable to Precharge Delay        | 40   |      | 1    | ns   |            |

| <sup>t</sup> OVH | Precharge & Cenable Overlap, High |      |      | 85   | ns   |            |

#### READ CYCLE

| SYMBOL                           | TEST                             | MIN. | TYP. | MAX. | UNIT | CONDITIONS                               |                            |

|----------------------------------|----------------------------------|------|------|------|------|------------------------------------------|----------------------------|

| <sup>t</sup> RC <sup>(1)</sup>   | Read Cycle                       | 300  |      |      | ns   | -                                        | }                          |

| <sup>t</sup> POV                 | Precharge to End of Cenable      | 115  | }    | 500  | ns   |                                          |                            |

| t <sub>PO</sub> (1)              | End of Precharge to Output Delay |      | 1    | 75   | ns   |                                          | t <sub>τ</sub> = 20 ns     |

| <sup>t</sup> ACC1 <sup>(1)</sup> | Address to Output Access         | 150  | Í    |      | ns   | <sup>t</sup> ACmin <sup>+ t</sup> OVLmin | C <sub>LOAD</sub> = 50 pF  |

|                                  |                                  |      |      |      |      | + tpOmax + 2 t <sub>τ</sub>              | - R <sub>LOAD</sub> = 100Ω |

| tACC2 <sup>(1)</sup>             | Precharge to Output Access       | 180  |      |      | ns   | <sup>t</sup> PCmin <sup>+ t</sup> OVLmin | V <sub>REF</sub> = 80 mV   |

|                                  |                                  |      | ]    |      |      | + tpOmax + 2 t <sub>τ</sub>              |                            |

#### WRITE OR READ/WRITE CYCLE

| SYMBOL                          | TEST                             | MIN. | TYP. | MAX. | UNIT | CONDITIONS                 |

|---------------------------------|----------------------------------|------|------|------|------|----------------------------|

| tWC                             | Write Cycle                      | 340  |      |      | ns   |                            |

| <sup>t</sup> RWC <sup>(1)</sup> | Read/Write Cycle                 | 340  |      |      | ns   | $t_{\tau} = 20 \text{ ns}$ |

| tPW                             | Precharge to Read/Write Delay    | 115  |      | 500  | ns   | _                          |

| tWP                             | Read/Write Pulse Width           | 20   | 1    |      | ns   |                            |

| tw                              | Read/Write Set Up Time           | 20   |      |      | ns   |                            |

| tDW                             | Data Set Up Time                 | 40   | )    |      | ns   |                            |

| t <sub>DH</sub>                 | Data Hold Time                   | 10   |      |      | ns   |                            |

| <sup>t</sup> PO <sup>{1}</sup>  | End of Precharge to Output Delay | 6    | 1    | 75   | ns   | CLOAD = 50 pF              |

|                                 |                                  |      | ļ    |      |      | R <sub>LOAD</sub> = 100Ω   |

| tp                              | Time to Next Precharge           | 0    |      |      | ns   | VREF = 80 mV               |

| <sup>t</sup> CW                 | Read/Write Hold Time             | 1    |      | 15   | ns   |                            |

#### CAPACITANCE (note 2)

| SYMBOL           | TEST                    | MIN. | TYP. | MAX. | UNIT | CONDITIONS                                                                                          |

|------------------|-------------------------|------|------|------|------|-----------------------------------------------------------------------------------------------------|

| C <sub>AD</sub>  | Address Capacitance     |      | 5    | 7    | pF   | V <sub>IN</sub> = V <sub>SS</sub>                                                                   |

| CPR              | Precharge Capacitance   |      | 15   | 18   | pF   | V <sub>IN</sub> = V <sub>SS</sub>                                                                   |

| CCE              | Cenable Capacitance     |      | 15   | 18   | pF   | V <sub>IN</sub> = V <sub>SS</sub> f = 1 MHz                                                         |

| CRW              | Read/Write Capacitance  |      | 11   | 15   | рF   | VIN = VSS - All Unused Pins are                                                                     |

| CIN1             | Data Input Capacitance  |      | 4    | 5    | pF   | Cenable = 0V at A.C. Ground                                                                         |

| C <sub>IN2</sub> | Data Input Capacitance  |      | 2    | 4    | pF   | V <sub>IN</sub> = V <sub>SS</sub><br>Cenable = V <sub>SS</sub><br>V <sub>IN</sub> = V <sub>SS</sub> |

| COUT             | Data Output Capacitance |      | 2    | 3    | рF   | V <sub>OUT</sub> = 0V                                                                               |

These times will degrade by 35 ns if a V<sub>REF</sub> point of 40 mV is chosen instead of the 80 mV point defined in this specification.

This parameter is periodically sampled and is not 100% tested. It is measured at worst case operating conditions. Capacitance measurements for plastic packages only.

#### TIMING DIAGRAM

#### NOTES:

- 1 2 VDD + 2V  $t\tau$  is defined as the transitions between these two points. VSS - 2V

- tow is referenced to point (1) of the rising edge of cenable or read/write whichever occurs first. toH is referenced to point (2) of the rising edge of cenable or read/write whichever occurs first. ž

- 4

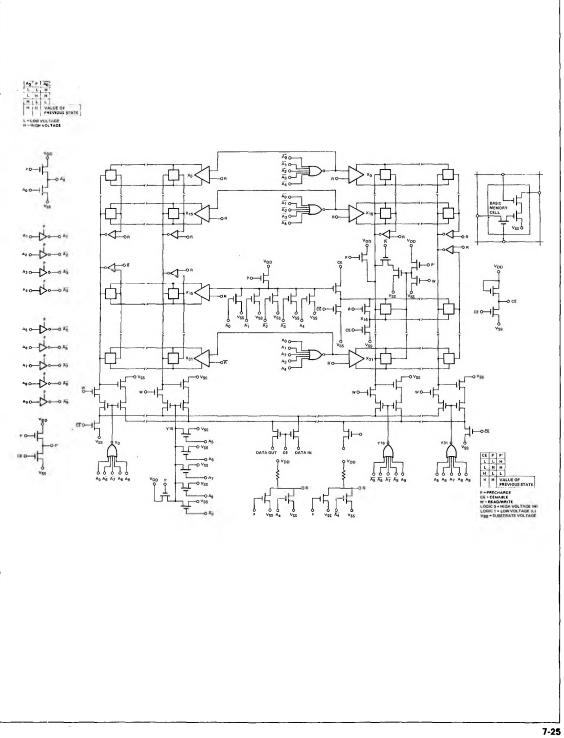

## CIRCUIT SCHEMATIC