# Zero-IF Tuner IC for Digital Satellite Broadcast

# CXD2832AER

### Description

The CXD2832AER is an IC developed for direct orthogonal detection of 1st IF signal (1 to 2 GHz) from RF converter block in a digital satellite broadcast receiver system. The CXD2832AER incorporates all the functions (LNA, RF gain control amplifier, VCO, mixer, baseband LPF, baseband gain control amplifier, tuning PLL) required for a satellite broadcast tuner.

#### Applications

- Digital TV

- ◆ STB for digital satellite broadcasting

- ◆ BD recorder

### Features

- Low noise figure : 5 dB (typ.)

- Low power consumption: 400 mW (typ.) (Includes internal LNA circuit)

- Clock output for a demodulator LSI

- Input pin for controlling of power saving mode

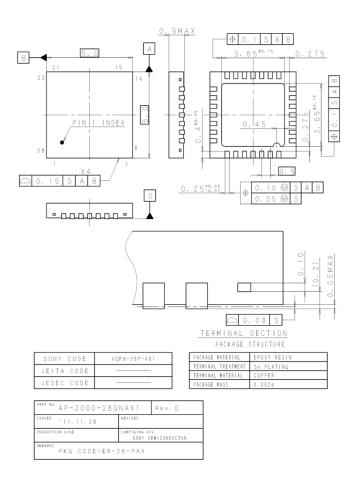

- Small package: 28 pin VQFN 5 mm × 5 mm (0.5 mm pitch)

#### **Absolute Maximum Ratings**

| <ul> <li>Supply voltage</li> </ul>      | $AV_{DD}, DV_{DD}$ | -0.3 to +3.6 | V (Ta = 25 °C) |

|-----------------------------------------|--------------------|--------------|----------------|

| <ul> <li>Storage temperature</li> </ul> | Tstg               | -55 to +150  | °C             |

### **Operating Conditions**

| <ul> <li>Supply voltage</li> </ul>              | $AV_{DD}, DV_{DD}$ | 2.375 to 3.465 V                                                   |

|-------------------------------------------------|--------------------|--------------------------------------------------------------------|

| <ul> <li>Operating temperature</li> </ul>       | Topr1              | -20 to +85 °C (AV <sub>DD</sub> , $DV_{DD} \le 2.8 \text{ V}$ )    |

| <ul> <li>Operating temperature</li> </ul>       | Topr2              | -20 to +75 °C (AV <sub>DD</sub> , DV <sub>DD</sub> > 2.8 V)        |

| <ul> <li>Allowable power dissipation</li> </ul> | on                 | 2.2 W (30 mm $\times$ 60 mm, t = 1.0 mm, mounted on 2 layer board) |

Note) This IC has pins whose electrostatic discharge strength is weak as the high-frequency process is used. Handle the IC with care. Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

| Contents                                                   |    |

|------------------------------------------------------------|----|

| Description                                                | 1  |

| Features                                                   | 1  |

| Absolute Maximum Ratings                                   | 1  |

| Operating Conditions                                       | 1  |

| Basic Specifications                                       | 3  |

| Pin configuration and Block Diagram                        | 4  |

| Pin Description and Input / Output Pin Equivalent Circuit  | 5  |

| Electrical Characteristics Measurement Circuit             | 9  |

| Electrical Characteristics                                 | 10 |

| DC and analog characteristics                              | 10 |

| Electrical Characteristics of Logic block                  | 13 |

| Power-on sequence                                          | 14 |

| Description of Operation                                   | 15 |

| Analog part                                                | 15 |

| Serial Bus Interface part                                  | 16 |

| Slave Address Selection                                    | 16 |

| Writing and reading procedure                              | 18 |

| Description of SCL and SDA Signal during Bus Communication | 18 |

| Detailed Description of Registers                          | 19 |

| Tuning Procedure                                           | 25 |

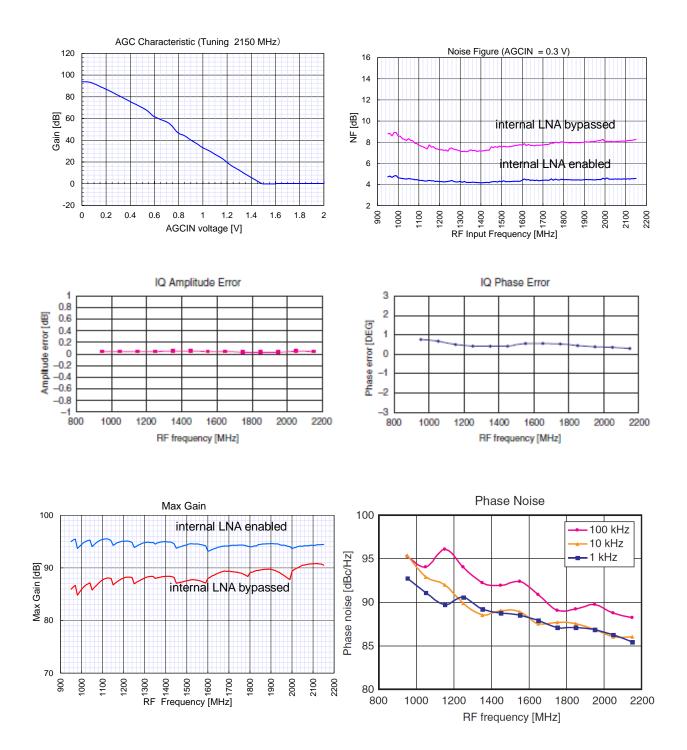

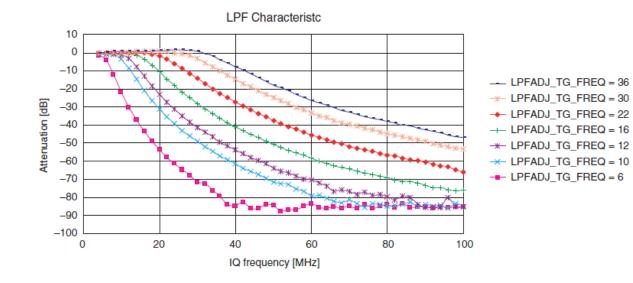

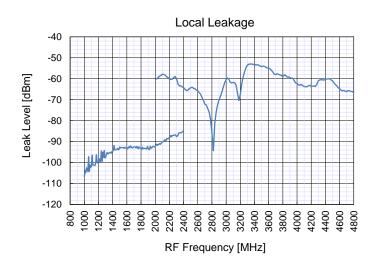

| Example of Representative Characteristics                  | 26 |

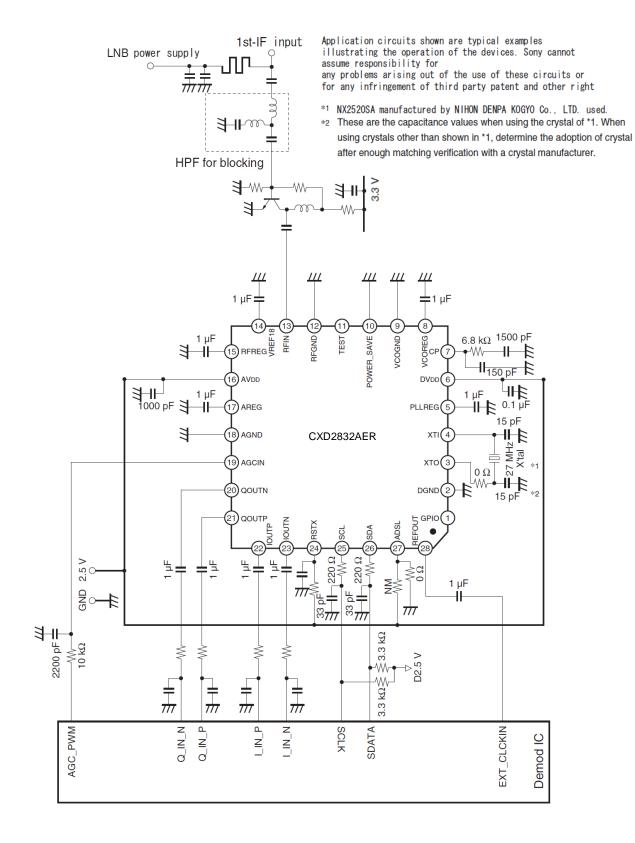

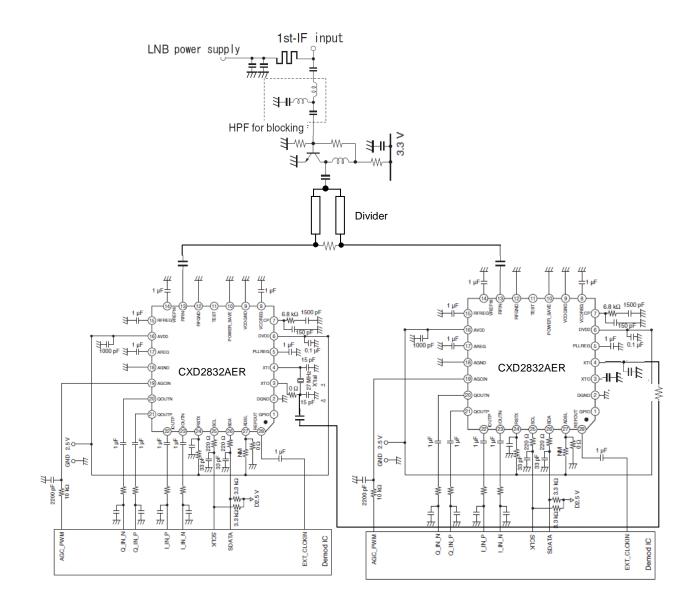

| Application Circuit                                        | 28 |

| Application for Single tuner                               | 28 |

| Application for double tuner                               | 29 |

| Package outline                                            | 30 |

| Marking                                                    | 30 |

# **Basic Specifications**

| Receiving frequency range      | 950 to 2150           | MHz  |

|--------------------------------|-----------------------|------|

| Input signal range             | -85 to -10            | dBm  |

| (internal LNA enabled)         |                       |      |

| Power supply voltage           | 2.5 or 3.3            | V    |

| Standard baseband output level | 0.7                   | Vp-р |

| Tuning frequency step          | 1                     | MHz  |

| (PLL comparison frequency)     |                       |      |

| Baseband bandwidth             | 5 to 36               | MHz  |

|                                | (1 MHz step variable) |      |

| Clock frequency                | 16 or 24 or 27        | MHz  |

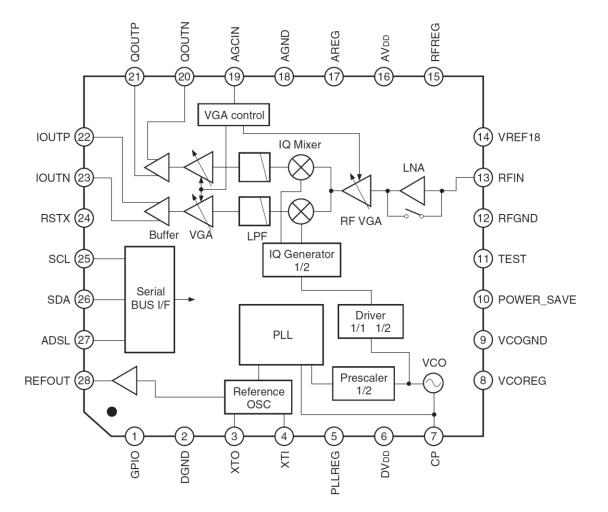

# Pin configuration and Block Diagram

#### **Description of Block Diagram**

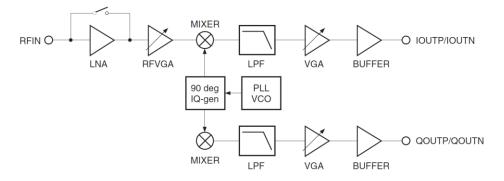

The block names shown in the block diagram above have the following functions.

| Reference OSC  | Crystal oscillation circuit for reference clock |

|----------------|-------------------------------------------------|

| Serial BUS I/F | Interface block for serial bus                  |

| PLL            | Tuning PLL                                      |

| Prescaler      | PLL fixed divider                               |

| VCO            | VCO circuit for local signal                    |

| Divider        | Frequency divider for local signal              |

| IQ Generator   | Frequency divider for IQ signal                 |

| LNA            | Low Noise Amplifier                             |

| RF VGA         | Gain control amplifier for RF signal            |

| IQ Mixer       | Quadrature demodulator (Mixer circuit)          |

| LPF            | Low Pass Filter                                 |

| VGA            | Gain control amplifier for baseband signal      |

| Buffer         | Output buffer circuit for baseband signal       |

| VGA control    | gain variation characteristic control circuit   |

# Pin Description and Input / Output Pin Equivalent Circuit

(Pin voltage shows typical DC voltage value when AGCI = 0 V)

| Pin<br>No | Symbol     | Pin<br>voltage [V] | Equivalent circuit                                                                                            | Description                                                                                                                                                                                                            |

|-----------|------------|--------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | GPIO       | 0/1.9              | 6 DVDD PLLREG 5<br>1 H H H H H H H H H H H H H H H H H H H                                                    | General purpose output                                                                                                                                                                                                 |

| 2         | DGND       | 0                  |                                                                                                               | GND Pin for PLL and logic circuits                                                                                                                                                                                     |

| 3, 4      | XTO<br>XTI | 0.6<br>0.6         | 6<br>DVDD<br>5<br>PLLREG<br>5<br>PLLREG<br>5<br>0 Ω<br>50 Ω<br>50 Ω<br>500 Ω<br>5<br>100 kΩ<br>4<br>2<br>DGND | Crystal oscillator connection for<br>reference clock.<br>When it is used as external clock<br>input instead of crystal<br>connection, please use XTI pin as<br>clock input, and connect XTO to<br>GND via capacitance. |

| 5         | PLLREG     | 1.9                | 6<br>DVDD<br>5<br>830 Ω<br>830 Ω<br>15 kΩ<br>2<br>DGND                                                        | External capacitor connection pin for regulator of PLL circuit. Please connect GND via capacitor of 1 $\mu$ F or more.                                                                                                 |

| 6         | DVDD       | 2.5                |                                                                                                               | PLL and logic power supply                                                                                                                                                                                             |

| 7         | СР         | 0.9                | 6 DVDD PLLREG<br>5<br>7 W W C<br>2 DGND                                                                       | Charge pump output for tuning<br>PLL                                                                                                                                                                                   |

| Pin<br>No | Symbol     | Pin<br>voltage [V] | Equivalent circuit                                                                                                                                                                            | Description                                                                                                                |

|-----------|------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 8         | VCOREG     | 1.9                | 6<br>DVDD<br>8<br>4<br>15 kΩ<br>5<br>9<br>VCOGND                                                                                                                                              | External capacitor connection pin<br>for regulator of VCO circuit.<br>Please connect GND via<br>capacitor of 1 μF or more. |

| 9         | VCOGND     | 0                  |                                                                                                                                                                                               | GND for VCO                                                                                                                |

| 10        | POWER_SAVE | 0/2.5/3.3          | 10<br>500 Ω<br>10<br>100 kΩ<br>2<br>DGND                                                                                                                                                      | Power save control pin.<br>Crystal oscillator stops and<br>internal circuit changes to power<br>saving mode when High.     |

| 11        | TEST       | 1.0                | $16 \xrightarrow{\text{AV}_{\text{DD}}} \xrightarrow{\text{RFREG}} 15$ $10 \text{ k}\Omega$ $11 \xrightarrow{\text{I}} 10 \text{ k}\Omega$ $12 \xrightarrow{\text{RFGND}} 10 \text{ k}\Omega$ | Test pin<br>No connect                                                                                                     |

| 12        | RFGND      | 0                  |                                                                                                                                                                                               | GND for RF circuits                                                                                                        |

| 13        | RFIN       | 0                  | 16<br>AVDD<br>13<br>T<br>RFGND<br>RFREG<br>15<br>T<br>T<br>RFREG<br>15<br>T<br>T<br>RFREG<br>T<br>S                                                                                           | Input for RF signal                                                                                                        |

| 14        | VREF18     | 1.8                | $16 \xrightarrow{\text{AVDD}} \xrightarrow{\text{AREG}} 17$ $16 \xrightarrow{\text{AVDD}} 1 \text{ k}\Omega$ $14 \xrightarrow{\text{S} 9 \text{ k}\Omega}$ $18 \xrightarrow{\text{AGND}}$     | Connecting capacitor for internal<br>reference voltage.<br>Please connect GND via<br>capacitor of 1 μF or more.            |

| Pin<br>No            | Symbol                           | Pin<br>voltage [V] | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Description                                                                                                                      |

|----------------------|----------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 15                   | RFREG                            | 2.0                | 16<br>4VDD<br>15<br>10 KΩ<br>10 KΩ<br>10 KΩ<br>10 KΩ<br>10 KΩ<br>10 KΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | External capacitor connection pin<br>for regulator of RF circuit.<br>Please connect GND via<br>capacitor of 1 μF or more.        |

| 16                   | AVDD                             | 2.5                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| 17                   | AREG                             | 2.0                | 16<br>4V <sub>DD</sub><br>17<br>10 kΩ<br>10 kΩ<br>18<br>AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | External capacitor connection pin<br>for regulator of base band circuit.<br>Please connect GND via<br>capacitor of 1 μF or more. |

| 18                   | AGND                             | 0                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND for analog circuits                                                                                                          |

| 19                   | AGCIN                            | 0 to 3.3           | 19 10 KΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Gain control pin for internal VGA circuits.                                                                                      |

| 20<br>21<br>22<br>23 | QOUTN<br>QOUTP<br>IOUTP<br>IOUTN | 1.0                | $\begin{array}{c} 16 \\ \hline AV_{DD} \\ \hline 22 \\ \hline 23 \\ \hline 23 \\ \hline 10 \\ \hline 4 \\ \hline 50 \\ \hline 10 \\ \hline 55 \\ \hline 10 \\ \hline 55 \\ \hline 10 \\ \hline 10 \\ \hline 55 \\ \hline 10 \\ $ | Baseband signal output                                                                                                           |

| Pin<br>No | Symbol | Pin<br>voltage [V] | Equivalent circuit                                                            | Description                                                                        |

|-----------|--------|--------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| 24        | RSTX   | Hi-Z               |                                                                               | Negative logic hardware reset pin<br>Hardware reset is necessary<br>when power up. |

| 25        | SCL    | Hi-Z               | 25<br>-500 Ω<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Clock input for serial bus                                                         |

| 26        | SDA    | Hi-Z               | 26<br>500 Ω<br>500 Ω<br>W<br>C<br>C<br>DGND                                   | Data input and output for serial<br>bus                                            |

| 27        | ADSL   | 0 to 2.2           | 6 DVDD PLLREG 5<br>30 kΩ<br>27                                                | Serial bus slave address setting                                                   |

| 28        | REFOUT | Hi-Z               | 6 DVDD PLLREG 5<br>28 W F<br>20 DGND                                          | Reference clock signal output                                                      |

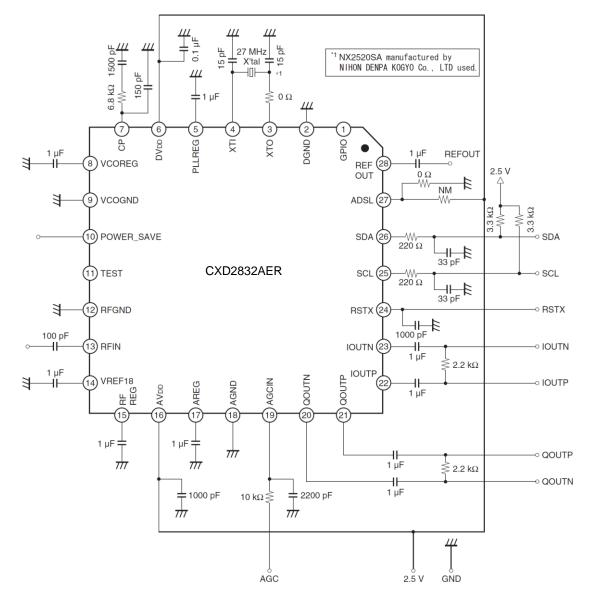

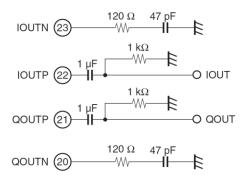

### **Electrical Characteristics Measurement Circuit**

Measurement circuit for single-end output.

### **Electrical Characteristics**

### DC and analog characteristics

See the Electrical Characteristics Measurement Circuit on page 9

Circuit voltage = 2.5 V, Ta = 25 °C

Unless otherwise specified the measuring condition is RF frequency = 2150 MHz, full gain (AGCI = 0 V)

DC Items

| Item                        | Symbol  | Condition                                           | Min | Тур. | Max | Unit |

|-----------------------------|---------|-----------------------------------------------------|-----|------|-----|------|

| Circuit current-1           | IDD-1   | Current at DV <sub>DD</sub> pin                     | 48  | 60   | 70  | mA   |

| Circuit current-2           | IDD-2   | Current at AV <sub>DD</sub> pin                     | 72  | 97   | 125 | mA   |

| Circuit current-3           | IDD-3   | Current at $AV_{DD}$ pin when internal LNA bypassed | 61  | 79   | 105 | mA   |

| Power save current 1        | PSIDD-1 | $DV_{DD}$ pin when clock is disabled                |     | 1    | 3   | mA   |

| Power save current 2        | PSIDD-2 | $AV_{DD}$ pin when LNA is enabled                   | 14  | 27   | 40  | mA   |

| Power save current 3        | PSIDD-3 | $AV_{DD}$ pin when LNA is bypassed                  | 3   | 9    | 20  | mA   |

| SDA, SCL, RSTX, POWER_SAVE  | E pin   |                                                     |     |      |     |      |

| High level input voltage    | VIH     |                                                     | 2.0 |      | 3.6 | V    |

| Low level input voltage     | VIL     |                                                     | GND |      | 1   | V    |

| SDA pin                     |         |                                                     |     |      |     |      |

| Low level output voltage    | VOL1    | Source current: 3 mA                                | GND |      | 0.4 | V    |

| GPIO pin                    |         |                                                     |     |      |     |      |

| High level output voltage   | VPH     | Source current: 3 mA                                | 1.7 | 1.9  | 2.1 | V    |

| Low level output voltage    | VPL     | Sink current:3 mA                                   | 0.0 |      | 0.2 | V    |

| Drive current               | IGD     | Source/Sink current                                 |     |      | 3   | mA   |

| AGCIN pin                   |         |                                                     |     |      |     |      |

| Input voltage range         | VIAH    |                                                     | 0   |      | 3.6 | V    |

| Input current               | ILAH    | AGCIN = 3.3 V                                       |     | 160  | 250 | μA   |

| OTHER                       |         |                                                     |     |      |     |      |

| Input current of RSTX pin   | ILRH    | Input Voltage = 3.3 V                               |     |      | 10  | μA   |

| Input current of POWER_SAVE | ILAH    | Input Voltage = 3.3 V                               |     |      | 10  | μA   |

### Analog Characteristics

Unless otherwise specified, AGCIN voltage that gives 0.7 Vp-pd differential output level

| Item               | Symbol | condition                                      | Min  | Тур | Max  | Unit   |

|--------------------|--------|------------------------------------------------|------|-----|------|--------|

|                    | RFIL1  | Internal LNA enabled                           | -85  |     | -10  | dBm    |

| Input level        | RFIL2  | Internal LNA bypassed                          | -75  |     | 0    | dBm    |

|                    | VIQ1   | Differential output *1                         |      |     | 1.5  | Vp-pd  |

| IQ output level    | VIQ2   | Single-end output *1                           |      |     | 1    | Vр-р   |

| IQ phase error     | EPH    | When RF input level is -40 dBm                 | -3.0 | 0   | +3.0 | deg    |

| IQ Amplitude error | EAMP   | When RF input level is -40 dBm                 | -1.0 | 0   | +1.0 | dB     |

|                    | NF1    | Internal LNA enabled                           |      | 5   | 8    | dB     |

| Noise Figure       | NF2    | Internal LNA bypassed                          |      | 8   | 12   | dB     |

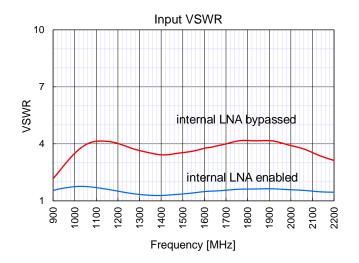

|                    | VSWR1  | Internal LNA enabled                           |      | 2   | 2.5  |        |

| RF input VSWR      | VSWR2  | Internal LNA bypassed                          |      | 3   | 4.5  |        |

|                    |        | When RF input level is -40 dBm                 |      |     |      |        |

|                    | PN1    | f <sub>RF</sub> = 2150 MHz                     | -89  |     | -85  | dBc/Hz |

| VCO phase noise    |        | 100 kHz offset                                 |      |     |      |        |

|                    | PN2    | 10 kHz offset                                  |      | -86 | -83  | dBc/Hz |

|                    | PN3    | 1 kHz offset                                   |      | -83 | -80  | dBc/Hz |

|                    |        | Internal LNA enabled                           |      |     |      |        |

|                    | IIP3L  | When desired signal input level is -20 dBm.    |      |     |      |        |

|                    |        | Calculated from IM3 measurement result by      |      | 9   |      | dBm    |

| IIP3               |        | 2 signals,                                     |      |     |      |        |

|                    |        | $f_{LO}$ + 5 MHz, $f_{LO}$ + 7 MHz             |      |     |      |        |

|                    | IIP3R  | Internal LNA bypassed                          |      | 10  |      | dBm    |

|                    | IIPSK  | Same measurement condition as IIP3L            | 12   |     |      | UDITI  |

|                    |        | Internal LNA enabled                           |      |     |      |        |

|                    |        | Calculates from IM2 by interference signal     |      |     |      |        |

|                    | IIP2L  | of 1040 MHz -20 dBm and 1100 MHz -20           |      | 14  |      | dBm    |

| IIP2               |        | dBm when setting desired signal                |      |     |      |        |

|                    |        | $f_{RF} = 2140 \text{ MHz} - 20 \text{ dBm}$   |      |     |      |        |

|                    | IIP2R  | Internal LNA bypassed                          |      | 30  |      | dBm    |

|                    |        | Same measurement condition as IIP2L            |      | 50  |      | ubiii  |

| RF Local Leak      | LOL    | Local OSC leak to RFIN                         | -    | -   | -65  | dBm    |

| PLL Reference Leak | REFL   | When $f_{REF} = 1 \text{ MHz}$                 | -    | -65 | -50  | dBc    |

| LPF attenuation 1  | LPFC1  | Attenuation at LPF setting value (fc)          | 8    | 5   | 1    | dB     |

| LPF attenuation 2  | LPFC2  | Attenuation at twice frequency of LPF setting. | 20   | 30  | 40   | dB     |

| Item                  | Symbol | condition                                               | Min  | Тур  | Max  | Unit |

|-----------------------|--------|---------------------------------------------------------|------|------|------|------|

| REF OUT Level         | ROL    | 1 kΩ loaded                                             | 0.3  | 0.6  | 0.8  | Vр-р |

| REFOUT maximum load   | ROD    | 1 kΩ loaded                                             |      |      | 20   | pF   |

|                       | VIXI1  | When using as external input (under $DV_{DD} = 0 v$ )   | 0    | -    | 0.70 | Vр-р |

| XTI pin input level   | VIXI2  | When using as external input (under $DV_{DD} = 2.5 V$ ) | 0.35 | 0.65 | 1.50 | Vр-р |

| External clock jitter | JIT    | When using as external input                            |      |      | 10   | ps   |

| XI pin capacitance    | CXI    | When using as external input                            |      |      | 5    | pF   |

\*1 IQ output level is defined with the output level that gives IM3 35 dB or more.

IM3 measurement condition is same as IIP3.

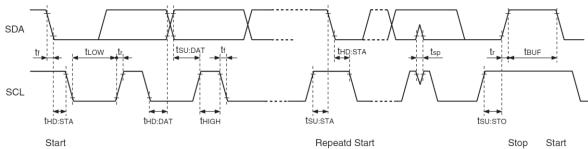

### **Electrical Characteristics of Logic block**

(Circuit voltage = 2.5 V, Ta = 25 °C)

| Item                                                         | Symbol              | condition             | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------|---------------------|-----------------------|------|------|------|------|

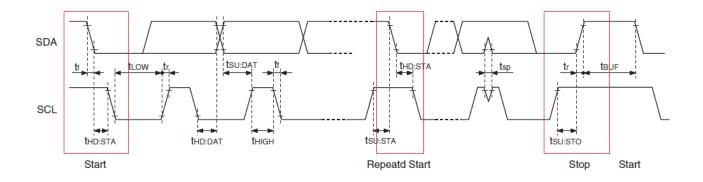

| SCL clock frequency                                          | f <sub>SCL</sub>    |                       | 0    |      | 400  | kHz  |

| Start - Hold time                                            | t <sub>HD:STA</sub> |                       | 600  |      |      | ns   |

| Stop - Setup time                                            | t <sub>SU:STO</sub> |                       | 600  |      |      | ns   |

| Bus free time between "STOP" condition and "START" condition | t <sub>BUF</sub>    |                       | 1300 |      |      | ns   |

| Data - Setup time                                            | t <sub>su:dat</sub> |                       | 100  |      |      | ns   |

| High hold time                                               | t <sub>HIGH</sub>   |                       | 600  |      |      | ns   |

| Data - Hold time                                             | t <sub>HD:DAT</sub> |                       | 0    |      | 900  | ns   |

| Low hold time                                                | t <sub>LOW</sub>    |                       | 1300 |      |      | ns   |

| Start - Setup time                                           | t <sub>SU:STA</sub> |                       | 600  |      |      | ns   |

| Rise time                                                    | tr                  |                       |      |      | 300  | ns   |

| Fall time                                                    | tf                  |                       |      |      | 300  | ns   |

| Spike pulse width                                            | T <sub>sp</sub>     |                       |      |      | 50   | ns   |

| Capacitive load of bus line                                  | C <sub>b</sub>      |                       |      |      | 400  | pF   |

| Hardware Reset pulse width                                   | t <sub>HR</sub>     | Input at 24pin (RSTX) | 1    |      |      | ms   |

tHD:STA = Hold time (repeated) START condition tLOW = LOW period of the SCL clock tHD:DAT = Data hold time tsu:DAT = Data setup time thigh = HIGH period of the SCL clock tsu:sta = Setup time for a repeated START condition  $t_{BUF} = Bus free time between a STOP and START condition$ tsu:sro = Setup time for STOP conditiontr = Rise time of both SDA and SCL signalstr = Fall time of both SDA and SCL signals

$^{\ast}$  When SCL falls, it means START condition if SDA is "0".

\* When SCL rises, it means STOP condition if SDA is "1".

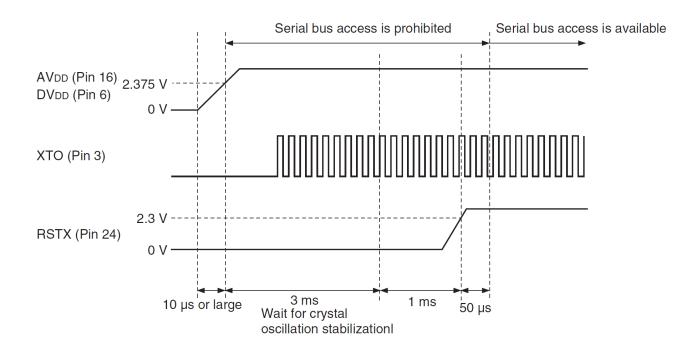

### **Power-on sequence**

The sequence from power-on to hardware reset is below.

Set RSTX low level for more than 1 ms or more after stability time of the crystal oscillation.

It is no problem which  $AV_{DD}$  (Pin 16) or  $DV_{DD}$  (Pin 6) start up first.

The communication of 2way serial bus is available after 50  $\mu$ s after canceling hardware reset.

#### **Description of Operation**

#### Analog part

The signal input to RFIN is converted to baseband I-Q signals by I-Q local signal which is generated by PLL circuit and output through buffer amplifier.

LNA : Single input internal LNA which input impedance is about 75  $\boldsymbol{\Omega}.$

RFVGA : In this block, RF gain control is performed.

This block has BPF characteristics to improve immunity to out-band interferer. Center frequency and gain of BPF should be optimized by register F\_CTL/G\_CTL based on tuning frequency.

The following settings are recommended.

| f <sub>RF</sub> < 975        | F_CTL = 11100 | G_CTL = 001 |

|------------------------------|---------------|-------------|

| 975 ≤ f <sub>RF</sub> < 1050 | F_CTL = 11000 | G_CTL = 010 |

| $1050 \le f_{RF} < 1150$     | F_CTL = 10100 | G_CTL = 010 |

| $1150 \le f_{RF} < 1250$     | F_CTL = 10000 | G_CTL = 011 |

| $1250 \le f_{RF} < 1350$     | F_CTL = 01100 | G_CTL = 100 |

| $1350 \le f_{RF} < 1450$     | F_CTL = 01010 | G_CTL = 100 |

| $1450 \le f_{RF} < 1600$     | F_CTL = 00111 | G_CTL = 101 |

| $1600 \le f_{RF} < 1800$     | F_CTL = 00100 | G_CTL = 110 |

| $1800 \le f_{RF} < 2000$     | F_CTL = 00010 | G_CTL = 110 |

| $2000 \leq f_{RF}$           | F_CTL = 00000 | G_CTL = 111 |

LPF: The LPF incorporates a 5th order low pass filter. It includes DC feedback circuit which reject DC offset. This DC feedback circuit requires no external capacitor, as it includes capacitor inside IC.

VGA: Base band gain control amplifier. It includes DC feedback circuit which reject DC offset.

This DC feedback circuit requires no external capacitor, as it includes capacitor inside IC.

Buffer: Differential output buffer for the baseband signal. It can be used as a single output IC by termination one side of the differential outputs by the recommended resistor and capacitor.

### Serial Bus Interface part

The internal registers of this IC are set via the 2-wire serial bus.

Registers that can be set via the bus have an 8-bit sub address, and this IC uses the sub addresses 00h to 7Fh. (See page

19 and onward for a detailed description of the registers.)

Continuous write and read are possible to registers with continuous sub addresses.

There is no limit to the number of words that can be continuously written or continuously read.

Write to read-only registers is ignored.

This serial bus can be set regardless of reference clock operation. In addition, the operation speed is also independent of the clock frequency.

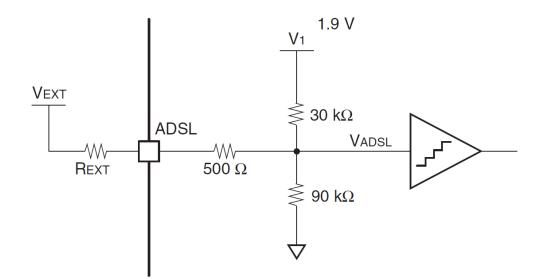

#### **Slave Address Selection**

Four different slave addresses can be selected by the voltage applied to the ADSL pin to support mounting of multiple tuner ICs.

WRITE mode that sets various data and READ mode that transmits the IC internal register data to the host side are switched by setting the LSB (R/W bit) of the address byte.

Slave addresses

| 1 | 1 | 0 | 0 | 0 | MA1 | MAO | R/W |

|---|---|---|---|---|-----|-----|-----|

MA1, MA0 : Portion that changes according to the ADSL pin voltage R/W : WRITE mode and READ mode switching R/W = "0" WRITE mode

R/W = "1" READ mode

| ADSL pin voltage | MA1 | MA0   |

|------------------|-----|-------|

| 0 to 0.19 V      | 0   | 0     |

| 0.4 to 0.6 V     | 0   | 1     |

| 0.8 to 1.1 V     | 1   | 0     |

| Open             | int | nibit |

| 1.71 to 2.2 V    | 1   | 1     |

ADSL Pin voltage is generated by the connection of resistor below.

| Slave<br>Address | ADSL<br>Pin voltage (V) | Connection of resistor                                            | recommended Value of $R_{EXT}$ ( $\Omega$ ) |

|------------------|-------------------------|-------------------------------------------------------------------|---------------------------------------------|

| C0               | 0 to 0.19               | Connect to GND                                                    | 0                                           |

| C2               | 0.4 to 0.6              | Connect to GND via R <sub>EXT</sub>                               | 10 k                                        |

| C4               | 0.8 to 1.1              | Connect to GND via R <sub>EXT</sub>                               | 47 k                                        |

|                  | 1.71 to 2.2             | Connect to PLLREG                                                 | 0                                           |

| C6               | 1.71 to 2.2             | Connect to $V_{DD}$ via $R_{EXT}$<br>(in case of $V_{DD}$ =2.5 V) | 22 k or 33 k                                |

|                  | 1.71 to 2.2             | Connect to $V_{DD}$ via $R_{EXT}$<br>(in case of $V_{DD}$ =3.3 V) | 47 k, or 68 k                               |

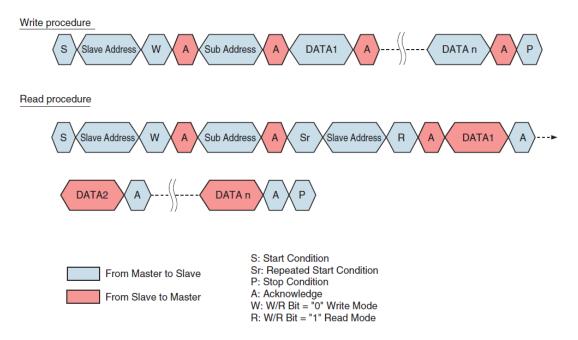

#### Writing and reading procedure

Writing register is performed as follows.

Write slave address -> Write desired sub address -> Write register setting value

This procedure is also applied to continuous write mode that performs continuous write to consecutive sub addresses. Reading register is performed in 1-byte units as follows.

Write slave address -> Write desired sub address -> Repeated start condition -> Write slave address -> Data read Repeated start condition can be substituted by "Stop condition -> Start condition".

This procedure is also applied to continuous read mode that performs continuous read form consecutive sub address.

#### Description of SCL and SDA Signal during Bus Communication

Start/Stop/Repeated start conditions signals are as shown in the figure below see the specifications for the detail timing.

# **Detailed Description of Registers**

| The data noted for each register are the initial values for this | IC. |

|------------------------------------------------------------------|-----|

|------------------------------------------------------------------|-----|

| Sub     | Desister nome  | Dit | DW | Bit position |   |   | Description |   |   |   |   |                                                                                                                                                                                                                                                                                                                                        |

|---------|----------------|-----|----|--------------|---|---|-------------|---|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address | Register name  | Bit | RW | 7            | 6 | 5 | 4           | 3 | 2 | 1 | 0 | Description                                                                                                                                                                                                                                                                                                                            |

| 00      | P_COUNT_H[7:0] | 8   | RW | 0            | 0 | 0 | 0           | 1 | 0 | 0 | 0 | PLL main counter frequency division ratio                                                                                                                                                                                                                                                                                              |

| 01      | P_COUNT_L[3:0] | 4   | RW | 1            | 0 | 0 | 1           |   |   |   |   | setting<br>P_COUNT = {P_COUNT_H[7:0],<br>P_COUNT_L [3:0]}<br>The settings to the internal counters are<br>executed when<br>they are written to sub address 03h.<br>* Initial value: 12'd137                                                                                                                                            |

|         | S_COUNT[2:0]   | 3   | RW |              |   |   |             | 1 | 0 | 0 |   | PLL swallow counter frequency division ratio setting * Initial value: 3'd4                                                                                                                                                                                                                                                             |

|         | RESERVE        | 1   | RW |              |   |   |             |   |   |   | 0 | RESERVE                                                                                                                                                                                                                                                                                                                                |

| 02      | K_COUNT_H[7:0] | 8   | RW | 0            | 0 | 0 | 0           | 0 | 0 | 0 | 0 | Test register.                                                                                                                                                                                                                                                                                                                         |

| 03      | K_COUNT_L[7:0] | 8   | RW | 0            | 0 | 0 | 0           | 0 | 0 | 0 | 0 | Always set to 00h<br>The values of sub Address 00 to 01<br>(P_COUNT/S_COUNT) are set when 00h is<br>written to sub address 03h.<br>So write 00h to 03h continuously when set<br>reception frequency.                                                                                                                                   |

| 04      | MDIV_SW        | 1   | RW | 0            |   |   |             |   |   |   |   | $\label{eq:When MDIV_SW} \begin{split} & \text{When MDIV_SW} \text{ is enabled, the frequency} \\ & \text{division ratio between the VCO and the} \\ & \text{MIXER changes from} \\ & 1/2 \text{ to } 1/4. \\ & 0:Thru. (1155 MHz $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $ $$                                                               |

|         | RESERVE[6:0]   | 7   | RW |              | 0 | 0 | 0           | 0 | 0 | 0 | 0 | RESERVE                                                                                                                                                                                                                                                                                                                                |

| 05      | CALIB_START    | 1   | RW | 0            |   |   |             |   |   |   |   | Calibration start bit. When "1" is set, the<br>CALIB sequence starts and the optimum<br>VCO selection, LPF cut off frequency and<br>CP current setting value are calculated.<br>Always execute calibration when changing<br>the tuning data.<br>1: Calibration start; this bit automatically<br>returns to "0" after calibration ends. |

|         | RESERVE[6:0]   | 7   | RW |              | 0 | 0 | 0           | 0 | 0 | 0 | 0 | RESERVE                                                                                                                                                                                                                                                                                                                                |

| 06      | REF_R[7:0]     | 8   | RW | 0            | 0 | 0 | 1           | 1 | 0 | 1 | 1 | PLL comparison frequency setting register.<br>*Initial value: 8'd27                                                                                                                                                                                                                                                                    |

| 07      | FIN[7:0]       | 8   | RW | 0            | 0 | 0 | 1           | 1 | 0 | 1 | 1 | Reference clock frequency (crystal<br>oscillation frequency) setting register<br>This is used as the frequency division ratio<br>for the system clock (1 MHz) required by the<br>logic block.<br>*Initial value: 8'd27                                                                                                                 |

| 08      | LT_EN          | 1   | RW | 1            |   |   |             |   |   |   |   | Test register<br>Please set 0.                                                                                                                                                                                                                                                                                                         |

|         | RESERVE[6:0]   | 7   | RW |              | 0 | 0 | 0           | 0 | 0 | 0 | 0 | RESERVE                                                                                                                                                                                                                                                                                                                                |

| 09      | G_CTL[2:0]     | 3   | RW | 0            | 0 | 0 |             |   |   |   |   | RFVGA gain control<br>This must be set according to the reception<br>frequency.<br>Max. gain 000<br>Min. gain 111                                                                                                                                                                                                                      |

|         | F_CTL[4:0]     | 5   | RW |              |   |   | 0           | 0 | 0 | 0 | 0 | RFVGA peak frequency control<br>This must be set according to the reception<br>frequency. (See page 13)<br>0000: high freq., 11111: low freq                                                                                                                                                                                           |

| Sub     | Desister        | D!  | DW |   |   | Bi | t po | sitio | on |   |   | Description                                                                                                                                                                                                                                  |

|---------|-----------------|-----|----|---|---|----|------|-------|----|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| address | Register name   | Bit | RW | 7 | 6 | 5  | 4    | 3     | 2  | 1 | 0 | Description                                                                                                                                                                                                                                  |

| 0A      | OUT_LEVEL[1:0]  | 2   | RW | 0 | 0 |    |      |       |    |   |   | IQ output gain and output type selection.<br>In case of using single end output, set 2'b01<br>or 2'b11.<br>00: Default (Differential output)<br>01: Single end output (+ 4.4 dB)<br>10: Reserve<br>11: Single end output (-2.4 dB)           |

|         | HP_MODE         | 1   | RW |   |   | 0  |      |       |    |   |   | Pass bandwidth control of DC feedback<br>0: normal<br>1: Low                                                                                                                                                                                 |

|         | GAIN_STEP[1:0]  | 2   | RW |   |   |    | 0    | 0     |    |   |   | Test register                                                                                                                                                                                                                                |

|         | RESERVE[2:0]    | 3   | RW |   |   |    |      |       | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 0B      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 0C      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 0D      | PORT            | 1   | RW | 0 |   |    |      |       |    |   |   | RESERVE                                                                                                                                                                                                                                      |

| 00      | RESERVE[6:0]    | 7   | RW |   | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

|         | REFOUTEN        | 1   | RW | 1 |   |    |      |       |    |   |   | REFOUT circuit enable<br>* 1: Enable<br>0: Disable                                                                                                                                                                                           |

| 0E      | XOSC_SEL[4:0]   | 5   | RW |   | 1 | 1  | 1    | 1     | 1  |   |   | Crystal oscillator drive current setting<br>register, 1 LSB = 25 $\mu$ A (Max: 775 $\mu$ A).<br>The crystal oscillator is stopped and external<br>clock input is available by setting 5'b0_0000.<br>* Initial value: 5'b1_1111 (775 $\mu$ A) |

|         | RESERVE[1:0]    | 2   | RW |   |   |    |      |       |    | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 0F      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 10      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

|         | PS_EN           | 1   | RW | 0 |   |    |      |       |    |   |   | Power save setting<br>0: Reception (Normal status)<br>1: Powe saving                                                                                                                                                                         |

| 11      | PS_XOSC_EN      | 1   | RW |   | 0 |    |      |       |    |   |   | Crystal oscillator operating setting when<br>PS_EN = H<br>0: Stop crystal oscillation<br>1: Continuos oscillation                                                                                                                            |

|         | RESERVE[5:0]    | 6   | RW |   |   | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

|         | LNASW           | 1   | RW | 0 |   |    |      |       |    |   |   | Internal LNA setting<br>0: Internal LNA ON<br>1: LNA bypassed                                                                                                                                                                                |

|         | LNA_IADJ        | 1   | RW |   | 0 |    |      |       |    |   |   | Test register                                                                                                                                                                                                                                |

|         | IT_MODE         | 1   | RW |   |   | 1  |      |       |    |   |   | Test register                                                                                                                                                                                                                                |

|         | RFREG_VADJ[1:0] | 2   | RW |   |   |    | 0    | 0     |    |   |   | Test register                                                                                                                                                                                                                                |

| 12      | LNA_EN          | 1   | RW |   |   |    |      |       | 1  |   |   | Enabler of LNA circuit<br>0: LNA Disable<br>1: LNA Enable                                                                                                                                                                                    |

|         | RFVGA_EN        | 1   | RW |   |   |    |      |       |    | 1 |   | Enabler of RFVGA circuit.<br>0: RFVGA Disable<br>1: RFVGA Enable                                                                                                                                                                             |

|         | RFREG_EN        | 1   | RW |   |   |    |      |       |    |   | 1 | Enabler of regulator for RF circuits.<br>0: RFREG Disable<br>1: RFREG Enable                                                                                                                                                                 |

| 13      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| 14      | RESERVE[7:0]    | 8   | RW | 0 | 0 | 0  | 0    | 0     | 0  | 0 | 0 | RESERVE                                                                                                                                                                                                                                      |

| Sub     | Begister nome   | Bit | RW  |   |   | Bi | it po | sitio | on |   |   | Description                                                                                                            |

|---------|-----------------|-----|-----|---|---|----|-------|-------|----|---|---|------------------------------------------------------------------------------------------------------------------------|

| address | Register name   | ы   | RVV | 7 | 6 | 5  | 4     | 3     | 2  | 1 | 0 | Description                                                                                                            |

|         | BBTEST_EN[1:0]  | 2   | RW  | 0 | 0 |    |       |       |    |   |   | Test register                                                                                                          |

| 15      | MIX_EN          | 1   | RW  |   |   | 1  |       |       |    |   |   | Enabler of Mixer circuits.<br>0: Mixer Disable<br>1: Mixer Enable                                                      |