## ESM1602B

## QUAD COMPARATOR INTERFACE CIRCUIT

- MINIMUM HYSTERESIS VOLTAGE AT EACH INPUT: 0.3 V

- OUTPUT CURRENT: 15 mA

- LARGE SUPPLY VOLTAGE RANGE: + 10 V TO + 35 V

- INTERNAL THERMAL PROTECTION

- INPUT AND OUTPUT CLAMPING PROTEC-TION DIODES

#### DESCRIPTION

The ESM1602B is a quadruple comparator intended to provide an interface between signal processing and transmitting lines in very noisy industrial surroundings.

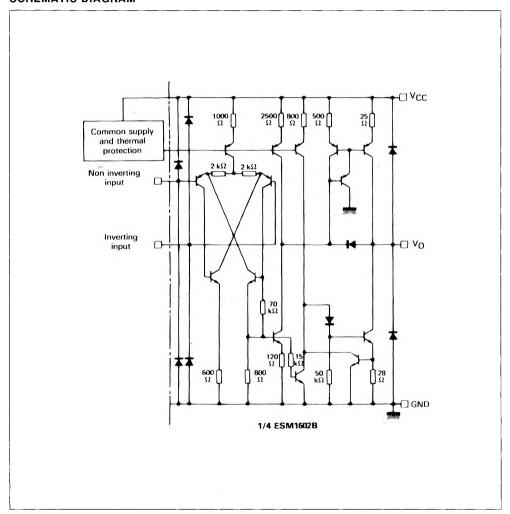

Output of each comparator, used as line driver, is well protected against powerful overvoltages. The output is a common emitter stage including complementary transistors. This arrangement ensures that no simultaneous conduction of high and low stages can occur in the presence of noise signals. Short-circuit currents toward  $V_{\rm CC}$  and ground are limited to the same value.

The ESM1602B can operate as receiver on a line transmitting noisy high-voltage signals. It has the same input stage as ESM1600B. Hysteresis effect, internally implemented on inputs of each comparator provides an excellent noise immunity. In addition each input is also protected against overvoltages.

The ESM1602B can operate in a wide supply voltage range (standard operational amplifier ± 15 V supply or single + 12 V or + 24 V supplies used in industrial electronic sets).

Moreover, internal thermal protection circuitry cuts out the output current of the four comparators when power dissipation becomes excessive.

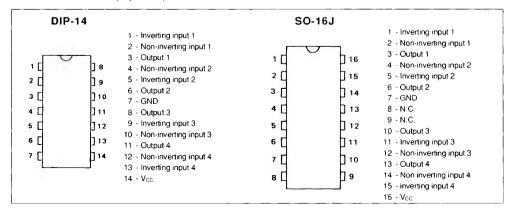

#### PIN CONNECTION (top view)

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol              | Parameter                           | Value              | Unit |  |

|---------------------|-------------------------------------|--------------------|------|--|

| Vcc                 | Supply Voltage                      | 45                 |      |  |

| V <sub>ID</sub>     | Differential Input Voltage          | 45                 | V    |  |

| Vı                  | Input Voltage                       | - 0.7 to + 45      | V    |  |

| I <sub>O(max)</sub> | Output Current                      | Internally Limited | mA   |  |

| P <sub>tot</sub>    | Power Dissipation                   | Internally Limited | W    |  |

| Top                 | Operating Ambient Temperature Range | - 25 to + 85       | °C   |  |

| T <sub>stg</sub>    | Storage Temperature Range           | - 40 to + 150      | °C   |  |

#### SCHEMATIC DIAGRAM

# **ELECTRICAL CHARACTERISTICS** $V_{CC}$ = + 35 $V_{v}$ - 25 $^{\circ}C \le T_{amb} \le$ + 85 $^{\circ}C$ (unless otherwise specified)

| Symbol                          | Parameter                                                                                 | Value  |         |          | Unit     | Fig.     |

|---------------------------------|-------------------------------------------------------------------------------------------|--------|---------|----------|----------|----------|

|                                 |                                                                                           | Min.   | Typ.    | Max.     | J        | g.       |

| V <sub>1</sub> <sup>+</sup>     | Input Voltage Range - Note 1                                                              |        |         |          | V        | _        |

| V <sub>i</sub> -                | Non-inverting Input<br>Inverting Input                                                    | 0<br>2 | _       | 33<br>33 |          |          |

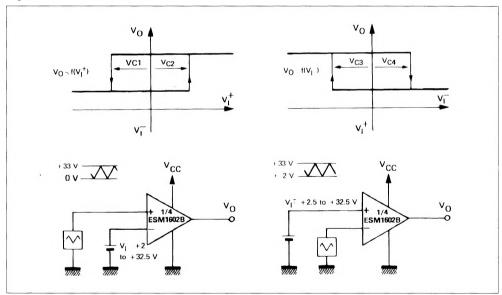

| $V_{\rm C}$                     | Input Control Voltage (2 V < V <sub>CM</sub> < 33 V) - Note 2                             | 150    | -       | 500      | mV       | 8        |

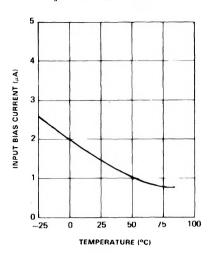

| I <sub>1B</sub>                 | Input Bias Current - Note 3                                                               | _      | 1       | 5        | μΑ       | <u> </u> |

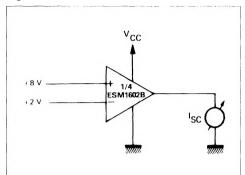

| Isc                             | Short-circuit Output Current<br>V <sub>CC</sub> = + 10 to + 35 V                          | 6      | _       | 25       | mA       | 9        |

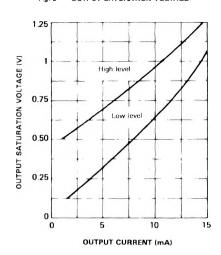

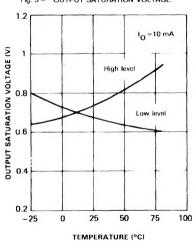

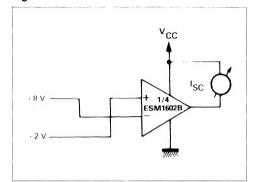

| V <sub>CC</sub> -V <sub>O</sub> | Output Saturation Voltage (high level) - (I <sub>O</sub> = - 10 mA)                       | _      | 1       | 1.5      | V        | 11       |

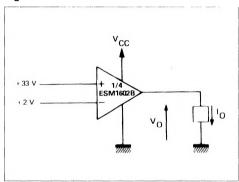

| Vo                              | Output Saturation Voltage (low level) - (I <sub>O</sub> = + 10 mA)                        | _      | 1       | 1.6      | V        | 12       |

| lcc                             | Supply Current                                                                            |        | -       |          | mA       |          |

|                                 | $R_L = \infty$ for the 4 Comparators<br>$R_L$ Common for the Comparators                  | _<br>_ | 4<br>10 | 6<br>13  |          | 13,14    |

| Svo                             | Output Slew-rate ( $R_L = 3 \text{ K}\Omega$ , $T_{amb} = + 25 \text{ °C}$ )              | 1      | -       | -        | V/µs     | _        |

| V <sub>F</sub>                  | Input Protective Diode Forward Voltage (I = 20 mA, T <sub>amb</sub> = + 25 °C)            | -      | _       | 1.5      | V        | -        |

| _                               | Energy of Pulses against which Circuit Output is<br>Protected                             |        |         |          | Lm       | -        |

|                                 | $(T_{amb} = + 25  ^{\circ}C) - Note 4$                                                    |        | -       | 20       | <u> </u> |          |

| _                               | Pulsed Current Applied to Protective Output Diodes $(T_{amb} = + 25  ^{\circ}C)$ - Note 5 | _      | 0.4     | _        | Α        | 15       |

Notes: 1. When negative input is biased between 0 and 2 volts output is always low.

- Comparator hysteresis voltage on positive input on the one hand and negative input on the other hand equals sum of input control voltages V<sub>C1</sub> + V<sub>C2</sub> or V<sub>C3</sub> + V<sub>C4</sub>.

- Input current flows out of the circuit owing to PNP input stage. This current is constant and independent of output level. So no load change is transmitted to inputs.

- 4. By definition, a circuit is immunized against powerful signals when no durable characteristic change occurs after the application of these signals and when the circuit has not been destroyed.

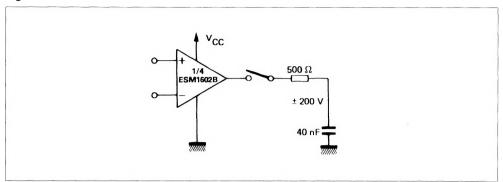

In industrial surroundings, parasitic signals contain usually high voltage (over 200 V) AC harmonics having variable impedance of

500 \( \Omega\_{10} \) 10 K\( \Omega\_{10} \). The power dissipation of these signals is divided between clamping diodes and the V<sub>CC</sub>. Simulation is used to determine the maximum energy level. The injected current value cannot in any case exceed 3 A.

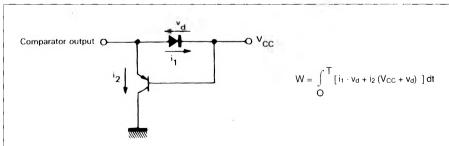

5. Output protective diodes are individually by means of positive and negative discharge voltages of a capacitor. The negative discharge control occurs through a single diode. During positive discharge, due to the properties of integration, a grounded collector PNP transistor appears in parallel with the clamping diode connected to V<sub>CC</sub>. A part of the current flows through this transistor, V<sub>CE</sub> being greater than V<sub>CC</sub>. If T is the total discharge duration, energy dissipated in the circuit is:

For a certain injected current, the lower the current I<sub>2</sub>, that is to say the lower the PNP current gain the smaller the energy is dissipated in the circuit. Topology and technological processes have been chosen to shorten this current gain.

Fig. 1 -- INPUT BIAS CURRENT.

Fig. 2 - OUTPUT SATURATION VOLTAGE

Fig. 3 - OUTPUT SATURATION VOLTAGE.

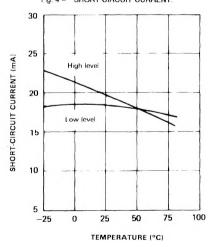

Fig. 4 - SHORT CIRCUIT CURRENT.

#### TYPICAL APPLICATIONS

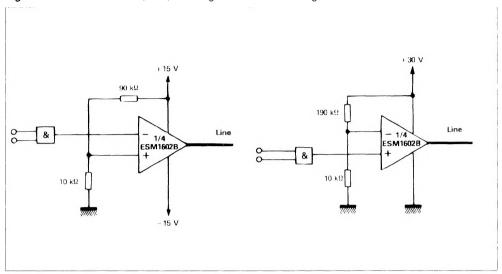

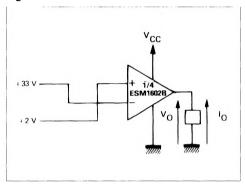

Figure 5: Conversion of DTL, TTL, MOS Signals on a Transmitting Line.

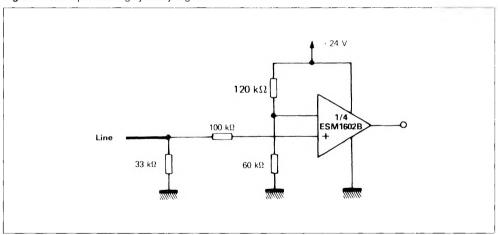

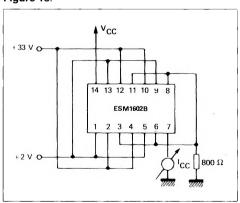

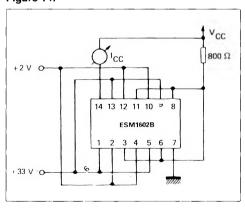

Figure 6: Reception of Highly Noisy Signals.

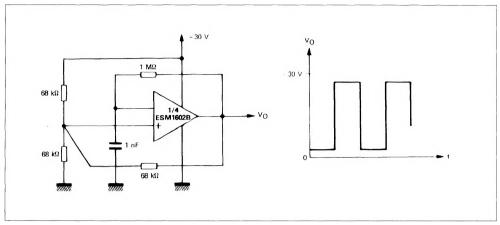

Figure 7: Free-running Square Wave Oscillator.

### **TEST CIRCUITS**

Figure 8.

Figure 9.

Figure 10.

Figure 11.

Figure 12.

Figure 13.

Figure 14.

Figure 15.

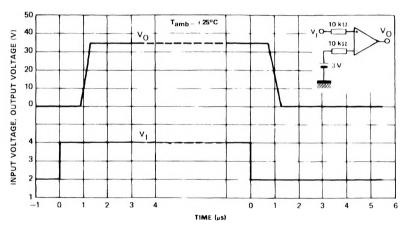

Figure 16: Response Time.