# Universal Peripheral Controller

#### **Features**

- Complete slave microcomputer, for distributed processing use.

- Unmatched power of Z8 architecture and instruction set.

- Three programmable I/O ports, two with optional 2-Wire Handshake.

- Six levels of priority interrupts from eight sources: six from external sources and two from internal sources.

- Two programmable 8-bit counter/timers

- each with a 6-bit prescaler. Counter/Timer T0 is driven by an internal source, and Counter/Timer T1 can be driven by internal or external sources. Both counter/timers are independent of program execution.

- 256-byte register file, accessible by both the master CPU and UPC, as allocated in the UPC program.

- 2K bytes of on-chip ROM for efficiency and versatility.

#### General Description

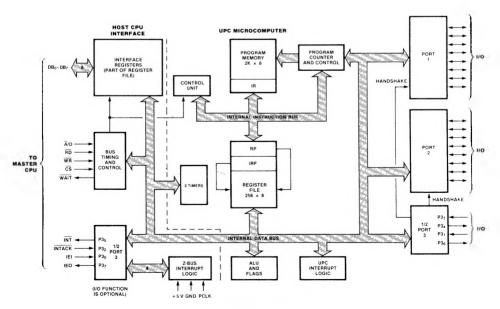

The Z8590 Universal Peripheral Controller (UPC) is an intelligent peripheral controller for distributed processing applications (Figure 3). The UPC unburdens the host processor by assuming tasks traditionally done by the host (or by added hardware), such as performing arithmetic, translating or formatting data, and controlling I/O devices. Based on the Z8 microcomputer architecture and instruction set, the UPC contains 2K bytes of internal pro-

gram ROM, a 256-byte register file, three 8-bit I/O ports, and two counter/timers.

The UPC offers fast execution time, an effective use of memory, and sophisticated interrupt, I/O, and bit manipulation. Using a powerful and extensive instruction set combined with an efficient internal addressing scheme, the UPC speeds program execution and efficiently packs program code into the on-chip ROM.

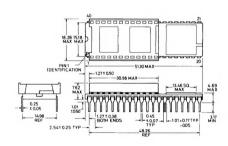

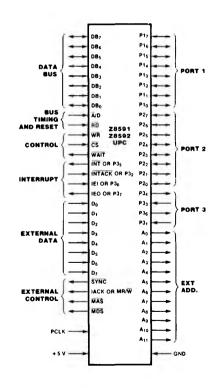

Figure 1. Z8590 UPC Logic Functions

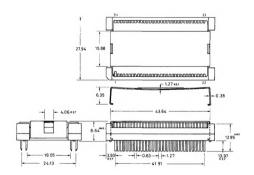

Figure 2. Z8590 UPC Pin Configuration

#### General Description (Continued)

An important feature of the UPC is an internal register file containing I/O port and control registers accessed both by the UPC program and indirectly by its associated master CPU. This architecture results in both byte and programming efficiency, because UPC instructions can operate directly on I/O data without moving it to and from an accumulator. Such a structure allows the user to allocate as many general purpose registers as the application requires for data buffers between the CPU and peripheral devices. All general-purpose registers can be used as address pointers, index registers, data buffers, or stack space.

The register file is logically divided into 16 groups, each consisting of 16 working registers. A Register Pointer is used in conjunction with short format instructions, resulting in tight, fast code and easy task switching.

Communication between the master CPU

and the register file takes place via one group of 19 interface registers addressed directly by both the master CPU and the UPC, or via a block transfer mechanism. Access by the master CPU is controlled by the UPC to allow independence between the master CPU and UPC software.

The UPC has 24 pins that can be dedicated to I/O functions. Grouped logically into three 8-line ports, they can be programmed in many combinations of input or output lines, with or without handshake, and with push-pull or open-drain outputs. Ports 1 and 2 are bit-programmable; Port 3 has four fixed inputs and four outputs.

To relieve software from coping with realtime counting and timing problems, the UPC has two 8-bit hardware counter/timers, each with a fixed divide-by-four, and a 6-bit programmable prescaler. Various counting modes may be selected.

Figure 3. Functional Block Diagram

## General Description (Continued)

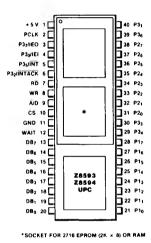

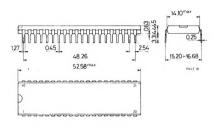

In addition to the 40-pin standard configuration, the UPC is available in four special configurations:

- A 64-pin RAM development version with external interface for up to 4K bytes of RAM and 36 bytes of internal ROM permitting down-loading from the master CPU.

- A Protopack RAM version with a socket for up to 2K bytes of RAM, with 36 bytes of internal ROM permitting down-loading from the master CPU.

- A 64-pin ROM development version with external interface for up to 4K bytes of ROM and no internal ROM.

- A Protopack ROM version with a socket for 2K bytes of ROM and no internal ROM.

This range of versions and configurations makes the UPC compatible with most system peripheral device control considerations.

#### Pin Description

Ā/D. Address/Data (input). A Low on this pin defines information on the data bus as an address. A High defines the information as data.

**CS.** Chip Select (input, active Low). A Low enables the UPC to accept address or data information from the master CPU during a write cycle or to transmit data to the master CPU during a read cycle. This line is usually generated from higher bits of the address lines.

**DB<sub>0</sub>-DB<sub>7</sub>.** Data Bus (bidirectional). This bus is used to transfer address and data information between the master CPU and the UPC.

Pl<sub>0</sub>-Pl<sub>7</sub>, P2<sub>0</sub>-P2<sub>7</sub>, P3<sub>0</sub>-P3<sub>7</sub>. I/O Port Lines (bidirectional, TTL compatible). These 24 lines are divided into three 8-bit I/O ports and may be configured in the following ways under program control:

**P1**<sub>0</sub>-**P1**<sub>7</sub>. *Port 1* (input/output—as output it can be push-pull or open-drain). Bit-programmable Parallel I/O.

**P20-P27.** Port 2 (input/output—as output, it can

be push-pull or open-drain). Bit-programmable Parallel I/O.

**P3<sub>0</sub>-P3<sub>7</sub>.** *Port 3* (four inputs, four outputs). Parallel I/O, handshake control, timer I/O, or interrupt control.

**PCLK.** Clock (input). TTL-compatible clock input, 4 MHz maximum. This signal does not need to be related to the master CPU clock.

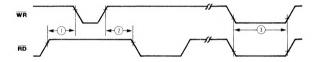

**RD.** Read (input, active Low). A Low enables the master CPU to read information from the UPC. Raising the voltage on this pin above  $V_{\text{DD}}$  will force the UPC into test mode.

**WAIT.** Wait (output, active Low, open-drain). When the CPU accesses the UPC register file, this signal requests the master CPU to wait until the UPC can complete its part of the transaction.

**WR.** Write (input, active Low). A Low on this pin enables the master CPU to write information to the UPC. A simultaneous Low on  $\overline{RD}$  and  $\overline{WR}$  resets the UPC. It is held in reset as long as  $\overline{WR}$  is Low.

# Functional Description

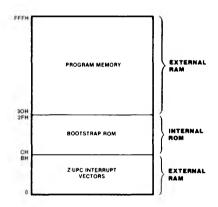

Address Space. On the 40-pin UPC, all address space is committed to on-chip memory. There are 2048 bytes of mask-programmed ROM and 256 bytes of register

file. I/O is memory-mapped to three registers in the register file. Only the Protopack and 64-pin versions of the UPC can access external program memory. See the section entitled

"Special Configurations" for complete descriptions of the Protopack and 64-pin versions. *Program Memory.* Figure 4 is a map of the 2K on-chip program ROM. Even though the architecture allows addresses from 0 to 4K, behavior of the device above program address 2047 (7FFH) is not defined. The first 12 bytes of program memory are reserved for the UPC interrupt vectors. For the Protopack and 64-pin

| 204                                                                    | 7  |                 |

|------------------------------------------------------------------------|----|-----------------|

| LOCATION OF<br>FIRST BYTE OF<br>INSTRUCTION<br>EXECUTED AFTER<br>RESET |    | USER<br>ROM     |

| NESEI                                                                  | 12 |                 |

|                                                                        | 11 | IRQ5 LOWER BYTE |

|                                                                        | 10 | IRQ5 UPPER BYTE |

|                                                                        | 9  | IRQ4 LOWER BYTE |

|                                                                        | 8  | IRQ4 UPPER BYTE |

|                                                                        | 7  | IRQ3 LOWER BYTE |

|                                                                        | 6  | IRQ3 UPPER BYTE |

|                                                                        | 5  | IRQ2 LOWER BYTE |

|                                                                        | 4  | IRQ2 UPPER BYTE |

|                                                                        | 3  | IRQ1 LOWER BYTE |

|                                                                        | 2  | IRQ1 UPPER BYTE |

|                                                                        | 1  | IRQ0 LOWER BYTE |

|                                                                        | 0  | IRQ0 UPPER BYTE |

Figure 4. Program Memory Map

versions, the address space is extended to 4096 bytes. In the RAM versions, addresses OCH through 2FH are reserved for on-chip ROM.

Register File. This 256-byte file includes three I/O port registers (1-3H), 234 general-purpose registers (6-EEH), and 19 control, status and special I/O registers (0H, 4H, 5H, and F0-FFH). The functions and mnemonics assigned to these register address locations are shown in Figure 5. Of the 256 UPC registers, 19 can be directly accessed by the master CPU; the others are accessed indirectly via the block transfer mechanism.

The I/O port and control registers are included in the register file without differentiation. This allows any UPC instruction to process I/O or control information, thereby eliminating the need for special I/O and control instructions. All general-purpose registers can function as accumulators, address pointers, or index registers. In instruction exe-

| OCATION  |                                  | (UPC Side |

|----------|----------------------------------|-----------|

| FFH      | STACK POINTER                    | SP        |

| FEH      | MASTER CPU INTERRUPT CONTROL     | MIC       |

| FDH      | REGISTER POINTER                 | RP        |

| FCH      | PROGRAM CONTROL FLAGS            | FLAGS     |

| FBH      | UPC INTERRUPT MASK REGISTER      | IMR       |

| FAH      | UPC INTERRUPT REQUEST REGISTER   | IRQ       |

| F9H      | UPC INTERRUPT PRIORITY REGISTER  | IPR       |

| F8H      | PORT 1 MODE                      | P1M       |

| F7H      | PORT 3 MODE                      | РЗМ       |

| F6H      | PORT 2 MODE                      | P2M       |

| F5H      | To PRESCALER                     | PRE0      |

| F4H      | TIMER/COUNTER 0                  | Τo        |

| F3H      | T <sub>1</sub> PRESCALER         | PRE1      |

| F2H      | TIMER/COUNTER 1                  | Т1        |

| F1H      | TIMER MODE                       | TMR       |

| FOH      | MASTER CPU INTERRUPT VECTOR REG. | MIV       |

| EFH      | GENERAL-PURPOSE REGISTERS        |           |

| 6H<br>5H | DATA INDIRECTION REGISTER        | DIND      |

| 4H       | LIMIT COUNT REGISTER             | LC        |

| 3Н       | PORT 3                           | P3        |

| 2H       | PORT 2                           | P2        |

| 1H       | PORT 1                           | PI        |

| ОН       | DATA TRANSFER CONTROL REGISTER   | DTC       |

Figure 5. Register File Organization

cution, the registers are read when they are defined as sources and written when defined as destinations.

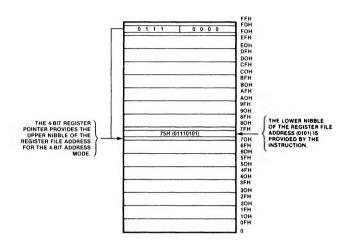

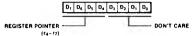

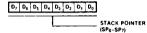

UPC instructions may access registers directly or indirectly using an 8-bit address mode or a 4-bit address mode and a Register Pointer. For the 4-bit addressing mode, the file is divided into 16 working register groups, each occupying 16 contiguous locations (Figure 6). The Register Pointer (RP) addresses the starting point of the active working-register group, and the 4-bit register designator supplied by the instruction specifies the register within the group. Any instruction altering the contents of the register file can also alter the Register Pointer. The UPC instruction set has a special Set Register Pointer (SRP) instruction for initializing or altering the pointer contents. Stacks. An 8-bit Stack Pointer (SP), register R255, is used for addressing the stack, residing within the 234 general-purpose

Figure 6. Register Pointer Mechanism

registers, address location 6H through EFH. PUSH and POP instructions can save and restore any register in the register file on the stack. During CALL instructions, the Program Counter is automatically saved on the stack. During UPC interrupt cycles, the Program Counter and the Flag register are automatically saved on the stack. The RET and IRET instructions pop the saved values of the Program Counter and Flag register.

**Ports.** The UPC has 24 lines dedicated to input and output. These are grouped into three ports of eight lines each and can be configured under software control as inputs, outputs, or special control signals. They can be programmed to provide Parallel I/O with or without handshake and timing signals. All outputs can have active pullups and pulldowns, compatible with TTL loads. In addition, they may be configured as open-drain outputs.

Port 1. Individual bits of Port 1 can be configured as input or output by programming

Port 1 Mode register (P1M) F8H. This port is accessed by the UPC program as general register 1H. It is written by specifying address 1H as the destination of any instruction used to store data in the output register. The port is read by specifying address 1H as the source of an instruction.

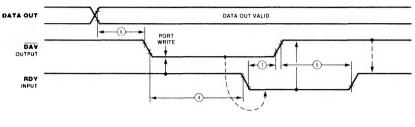

Port 1 may be placed under handshake control by programming Port 3 Mode register (P3M) F7H. This configures Port 3 pins P33 and P34 as handshake control lines  $\overline{DAV_1}$  and  $\overline{RDY_1}$  for input handshake, or  $\overline{RDY_1}$  and  $\overline{DAV_1}$  for output handshake, as determined by the direction (input or output) assigned to bit 7 of Port 1. The Port 3 Mode register also has a bit that programs Port 1 for open-drain output.

Port 2. Individual bits of Port 2 can be configured as inputs or outputs by programming Port 2 Mode register (P2M) F6H. This port is accessed by the UPC program as general register 2H, and its functions and methods of programming are the same as those of Port 1.

Port 3 pins  $P3_1$  and  $P3_6$  are the handshake lines  $\overline{DAV_2}$  and  $RDY_2$ , with the direction (input or output) determined by the state of bit 7 of the port. The Port 3 Mode register also has a bit used to program Port 2 for open-drain output.

Port 3. This port can be configured as I/O or control lines by programming the Port 3 Mode register. Port 3 is accessed as general register 3H. The directions of the eight data lines are fixed. Four lines, P30 through P33, are inputs, and the other four, P34 through P37, are outputs. The control functions performed by Port 3 are listed in Table 1.

**Counter/Timers.** The UPC contains two 8-bit programmable counter/timers, each driven by an internal 6-bit programmable prescaler.

The T1 prescaler can be driven by internal or external clock sources. The T0 prescaler is driven by an internal clock source. Both counter/timers operate independently of the processor instruction sequence to relieve the program from time-critical operations like event counting or elapsed-time calculation. T0 Prescaler register (PRE0) F5H and T1 Prescaler register (PRE1) F3H can be programmed to divide the input frequency of the source being counted by any number from 1 to 64. A

| Function                  | Line                                                  | Direction      | Signal                                                   |

|---------------------------|-------------------------------------------------------|----------------|----------------------------------------------------------|

| Handshake {               | P3 <sub>1</sub>                                       | In             | DAV <sub>2</sub> /RDY <sub>2</sub>                       |

|                           | P3 <sub>3</sub>                                       | In             | DAV <sub>1</sub> /RDY <sub>1</sub>                       |

|                           | P3 <sub>4</sub>                                       | Out            | RDY <sub>1</sub> /DAV <sub>1</sub>                       |

|                           | P3 <sub>6</sub>                                       | Out            | RDY <sub>2</sub> /DAV <sub>2</sub>                       |

| UPC Interrupt<br>Request* | P3 <sub>0</sub><br>P3 <sub>1</sub><br>P3 <sub>3</sub> | In<br>In<br>In | IRQ <sub>3</sub><br>IRQ <sub>2</sub><br>IRQ <sub>1</sub> |

| Counter/Timer {           | P3 <sub>1</sub>                                       | In             | T <sub>7N</sub>                                          |

|                           | P3 <sub>6</sub>                                       | Out            | T <sub>OUT</sub>                                         |

| Master CPU                | P3 <sub>5</sub>                                       | Out            | INT                                                      |

|                           | P3 <sub>2</sub>                                       | In             | INTACK                                                   |

|                           | P3 <sub>0</sub>                                       | In             | IEI                                                      |

|                           | P3 <sub>7</sub>                                       | Out            | IEO                                                      |

| Test Mode                 | P3 <sub>5</sub>                                       | Out            | Ā/D                                                      |

\*P3<sub>0</sub>, P3<sub>1</sub>, and P3<sub>3</sub> can always be used as UPC interrupt request inputs, regardless of the configuration programmed.

Table 1. Port 3 Control Functions

counter register (F2H or F4H) is loaded with a number from 1 to 256. The corresponding counter is decremented from this number each time the prescaler reaches end-of-count. When the count is complete, the counter issues a timer interrupt request;  $IRQ_4$  for T0 or  $IRQ_5$  for T1. Loading either counter with a number (n) results in the interruption of the UPC at the nth count.

The counters can be started, stopped, restarted to continue, or restarted from the initial value. They can be programmed to stop upon reaching end-of-count (Single-Pass mode) or to automatically reload the initial value and continue counting (Modulo-n Continuous mode). The counters and prescalers can be read at any time without disturbing their values or changing their counts. The clock sources for both timers can be defined as any one of the following:

- UPC internal clock (4 MHz maximum) divided by four.

- External clock input to Counter/Timer T1 via P3<sub>1</sub> (1 MHz maximum).

- Retriggerable trigger input for the UPC internal clock divided by four.

- Nonretriggerable trigger input for the UPC internal clock divided by four.

- External gate input for the UPC internal clock divided by four.

**Interrupts.** The UPC allows six interrupts from eight different sources as follows:

- Port 3 lines P3<sub>0</sub>, P3<sub>2</sub>, and P3<sub>3</sub>.

- The master CPU(3).

- The two counter/timers.

These interrupts can be masked and globally enabled or disabled using Interrupt Mask Register (IMR) FBH. Interrupt Priority Register (IPR) F9H specifies the order of their priority. All UPC interrupts are vectored.

Table 2 lists the UPC's interrupt sources, their types, and their vector locations in program ROM. Interrupt Request IRQ<sub>6</sub> is dedicated to master CPU communications.

| Name             | Source                                                | Vector<br>Location | Comments                                     |

|------------------|-------------------------------------------------------|--------------------|----------------------------------------------|

| $IRQ_0$          | EOM, XERR, LERR                                       | 0,1                | Internal (RO Bits 0, 1, 2)                   |

| $IRQ_1$          | $\overline{DAV}_1$ , $IRQ_1$                          | 2,3                | External (P33)   Edge Triggered              |

| $IRQ_2$          | DAV <sub>2</sub> , IRQ <sub>2</sub> , T <sub>IN</sub> | 4,5                | External (P3 <sub>1</sub> )   Edge Triggered |

| $IRQ_3$          | IRQ3, IEI                                             | 6,7                | External (P3 <sub>0</sub> )   Edge Triggered |

| IRQ <sub>4</sub> | TO                                                    | 8,9                | Internal                                     |

| IRQ <sub>5</sub> | Tl                                                    | 10,11              | Internal                                     |

Table 2. Interrupt Types, Sources, and Vector Locations

Interrupt Requests  $IRQ_1$ ,  $IRQ_2$ , and  $IRQ_3$  are generated on the falling transitions of external inputs  $P3_3$ ,  $P3_1$ , and  $P3_0$ . Interrupt Requests  $IRQ_4$  and  $IRQ_5$  are generated upon the timeout of the UPC's two counter/timers. When an interrupt request is granted, the UPC enters an interrupt machine cycle. This cycle disables all subsequent interrupts, saves the Program Counter and Status Flags, and branches to the program memory vector location reserved for that interrupt. This memory location and the next byte contain the I6-bit address of the interrupt service routine for that particular interrupt request.

The UPC also supports polled systems. To accommodate a polled structure, any or all of the interrupt inputs can be masked and the Interrupt Request register polled to determine which of the interrupt requests needs service.

Following any hardware reset operation, an EI instruction must be executed to enable the setting of any interrupt request bit in the IRQ register. Interrupts must be disabled prior to changing the content of either the IPR (F9H) or the IMR (FBH). DI is the only instruction that should be used to globally disable interrupts.

Master CPU Register File Access. There are two ways in which the master CPU can access the UPC register file: direct access and block access.

Direct Access. Three UPC registers—the Data Transfer Control (0H), the Master Interrupt Vector (F0H), and the Master Interrupt Control (FEH)—are mapped directly into the master CPU address space. The master CPU accesses these registers via the addresses shown in Table 3.

| UPC Ac<br>Decimal | idress<br>Hex | <b>Identifier</b> | Address   |

|-------------------|---------------|-------------------|-----------|

| 0                 | OH            | DTC               | xxx11000  |

| 5                 | 5H            | DIND              |           |

| <b>@</b> 5**      | @5H**         |                   | xxxlllll  |

| 240               | FOH           | MIV               | xxx10000  |

| 254               | FEH           | MIC               | xxx111110 |

| *n                |               | DSC0              | xxx00000  |

| n + l             |               | DSCI              | xxx00001  |

| n + 2             |               | DSC2              | xxx00010  |

| n + 3             |               | DSC3              | 11000xxx  |

| n + 4             |               | DSC4              | 00100xxx  |

| n + 5             |               | DSC5              | 10100xxx  |

| n + 6             |               | DSC6              | xxx00110  |

| n + 7             |               | DSC7              | xxx00111  |

| n + 8             |               | DSC8              | xxx01000  |

| n + 9             |               | DSC9              | xxx01001  |

| n + 10            |               | DSCA              | 01010xxx  |

| n + 11            |               | DSCB              | xxx01011  |

| n + 12            |               | DSCC              | xxx01100  |

| n + 13            |               | DSCD              | 10110xxx  |

| n + 14            |               | DSCE              | xxx01110  |

| n + 15            |               | DSCF              | xxxOllll  |

x = don't care

Table 3. Master CPU/UPC Register Map

<sup>\*</sup>n is the value in the IRP x 16

<sup>\*\*</sup>Master CPU accesses the register address in Register 5.

The master CPU also has direct access to 16 registers known as the DSC (Data, Status, Command) registers. The DSC registers are numbered 0 through F (DSC0-DSCF). These registers can be any 16 contiguous register file registers beginning on a 16-byte boundary. The base address of the DSC register group is designated by the IRP (I/O Register Pointer), which is bits  $D_4$ - $D_7$  of the Data Transfer Control register (0H). Figure 7 shows how the register address is made up of the 4-bit IRP field, concatenated with the low order 4-bits of the address from the master CPU.

Block Access. The master CPU may transmit or receive blocks of data via address xxx11111. When the master CPU accesses this address. the UPC register pointed to by the Data Indirection register is read or written. The Data Indirection register is incremented, and the Limit Count register is decremented, for example, when the master CPU issues a read or write to address xxxlllll while the Data Indirection register contains the value 33H. The operation causes register 33H to be read or written and the Data Indirection register to be incremented to 34H. This scheme is well suited to Block I/O Instructions and allows the master CPU to efficiently read or write a block of data to or from the UPC.

The Limit Count register (04H) is decremented and is used to control the number of bytes to be transferred by master CPU block accesses. If the master CPU attempts a read or write to the UPC after the Limit Count register reaches 0, the access is

# Special Configurations

There are two piggyback and two 64-pin versions of the UPC. These versions are identical to the 40-pin UPC with the following exceptions:

■ Internal ROM is totally omitted from the 64-pin development (Z8591) and piggyback ROM (Z8593) versions.

not completed, the LERR bit  $(D_2)$  of the Data Transfer Control register is set (indicating a limit error), and the LERR error causes an  $IRQ_0$  interrupt request.

The IRP field of the Data Transfer Control register, the Data Indirection register, and the Limit Count register are not directly accessible to the master CPU and therefore must be set by the UPC. This allows the UPC to protect itself from master CPU errors and frees the master CPU from tracking the UPC's internal data layout.

Figure 7. DSC Register Addressing Scheme

- All but 36 bytes of internal ROM are omitted from the 64-pin RAM (Z8592) and piggyback (RAM) (Z8594) versions.

- The memory address and data lines are buffered and brought out to external pins or to the socket on the piggyback.

- Control lines for the external memory are also provided.

#### Special Configurations (Continued)

The 64-pin version of the UPC allows the user to prototype the system in hardware with an actual UPC device and to develop the code intended to be mask programmed into the on-chip ROM of the 40-pin UPC for the production system. The 64-pin or piggyback RAM versions of the UPC are extremely versatile parts. Memory space can be extended to 4K bytes on the 64-pin version by using external RAM/ROM for all but 36 bytes of the UPC's memory space. This memory can then be down-loaded from the master CPU using a bootstrap program stored in the 36 bytes (C-2F). Figure 8 is a memory map for the 64-pin RAM version.

Figure 8. UPC RAM Version Memory Map

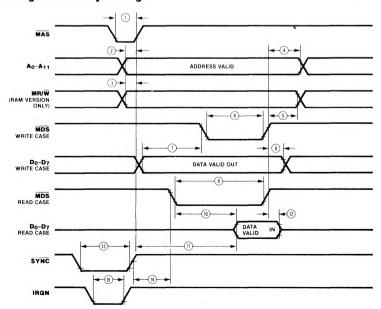

**64-Pin and Piggyback Pin Functions.** Forty of the pins on the 64-pin and piggyback versions have functions identical to those of the 40-pin version. The remaining 24 pins have additional functions described below. (Figures 9 through 11 show the 64-pin and piggyback versions' pin functions and pin assignments.)

**A<sub>0</sub>-A<sub>11</sub>.** Program Memory Address Lines (output). These lines are identical in all 64-pin and RAM versions in the piggyback. They are used to address 4K bytes of external UPC memory.

**D<sub>0</sub>-D<sub>7</sub>.** Program Data (input). Data is read in from the external memory on these lines. The RAM version also writes external memory through this bus.

**IACK.** Interrupt Acknowledge (output, active High). This signal is active whenever an internal UPC interrupt cycle is in process.

**MAS.** Memory Address Strobe (output, active Low). This address strobe is pulsed once for each memory fetch to interface with quasistatic RAM.

**MDS.** Memory Data Strobe (output, active Low). This signal is Low during an instruction fetch or memory write.

Figure 9. Z8591/Z8592 UPC Logic Functions

### Special Configurations (Continued)

MR/W. Memory Read/Write (output RAM versions only). This signal is High when the UPC is fetching an instruction and Low when it is loading external memory.

| P31[ 1                |       | 64 ]+5 V             |

|-----------------------|-------|----------------------|

| P36                   |       | 63 PCLK              |

| P27 [ 3               |       | 62 P37/IEO           |

| P26 [ 4               |       | 61 P30/IEI           |

| P25[ 5                |       | 60 P3VINT            |

| P24 ☐ 6               |       | 59 P32/INTACK        |

| P23[ 7                |       | 58 ] RD              |

| P22                   |       | 57 WR                |

| P21 [ 9               |       | 56 ] A/D             |

| P2₀ [ 10              |       | 55 CS                |

| P3 <sub>3</sub> [] 11 |       | 54 WAIT              |

| P34 [ 12              |       | 53 DB7               |

| P17 [ 13              |       | 52 DB6               |

| P16 [ 14              | Z8591 | 51 DBs               |

| P15[ 15               | Z8591 | 50 ] DB4             |

| P14 [ 16              | UPC   | 49 🔲 DB3             |

| P13[ 17               |       | 48 ] GND             |

| P12 ☐ 18              |       | 47 DB2               |

| P11[ 19               |       | 46 DB1               |

| P1o  20               |       | 45 DBo               |

| D7 [] 21              |       | 44 SYNC              |

| D <sub>6</sub> [ 22   |       | 43 MAS               |

| D <sub>5</sub> [ 23   |       | 42 MDS               |

| D4 [ 24               |       | 41 MR/W/IACK         |

| A <sub>0</sub> [ 25   |       | 40 ] D <sub>0</sub>  |

| A1 26                 |       | 39 🔲 D1              |

| A <sub>2</sub> [ 27   |       | 38 D2                |

| A3 28                 |       | 37 🗀 D3              |

| A4 🛛 29               |       | 36 A11               |

| A <sub>5</sub> [ 30   |       | 35 🔲 A <sub>10</sub> |

| A <sub>6</sub> [ 31   |       | 34 ] A <sub>9</sub>  |

| A, 🗀 32               |       | 33 🗀 🗛               |

|                       |       |                      |

Figure 10. Z8591/Z8592 UPC Pin Configuration

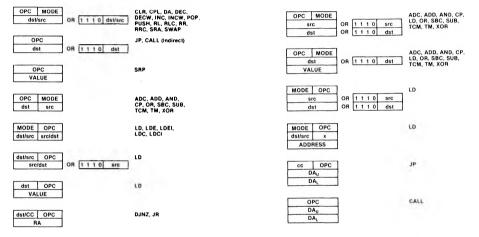

#### **Addressing Modes**

The following notation is used to describe the addressing modes and instruction operations as shown in the instruction summary.

- R Register or working-register address

- r Working-register address only

- IR Indirect-register or indirect working-register address

- Ir Indirect working-register address only

**SYNC.** Instruction Sync (output, active Low). This signal is Low during the clock cycle just preceding an opcode fetch.

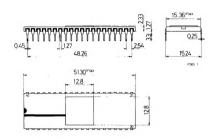

Figure 11. Z8593/Z8594 UPC Piggyback EPROM/RAM Pin Configuration

- RR Register pair or working-register pair address

IRR Indirect register pair or indirect working-register

- Irr Indirect working-register pair only

- X Indexed address

pair address

- DA Direct address

- RA Relative address

- IM Immediate

#### **Additional Symbols**

dat Destination location or contents

src Source location or contents

cc Condition code (see list)

Indirect address prefix

SP Stack Pointer (control register FFH)

PC Program Counter

FLAGS Flag register (control register FCH)

RP Register Pointer (control register FDH)

IMR Interrupt Mask register (control register FBH)

Assignment of a value is indicated by the symbol "-". For example,

dst + dst + src

indicates that the source data is added to the destination data and the result is stored in the destination location. The notation "addr(n)" is used to refer to bit "n" of a given location. For example,

dst (7)

refers to bit 7 of the destination operand.

#### Flags

Control Register FCH contains the following six flags:

C Carry flag

Zero flag

**S** Sign flag

V Overflow flag

D Decimal-adjust flag

H Half-carry flag

#### Affected flags are indicated by:

O Cleared to zero

Set to one

\* Set or cleared according to operation

Unaffected

Undefined

#### **Condition Codes**

| Value | Value Mnemonic Meaning |                                | Flags Set               |

|-------|------------------------|--------------------------------|-------------------------|

| 1000  |                        | Always true                    |                         |

| 0111  | С                      | Carry                          | C = 1                   |

| 1111  | NC                     | No carry                       | C = 0                   |

| 0110  | Z                      | Zero                           | Z = 1                   |

| 1110  | NZ                     | Not zero                       | Z = 0                   |

| 1101  | PL                     | Plus                           | S = 0                   |

| 0101  | MI                     | Minus                          | S = 1                   |

| 0100  | $\circ v$              | Overflow                       | V = 1                   |

| 1100  | NOV                    | No overflow                    | V = 0                   |

| 0110  | EQ                     | Equal                          | Z = 1                   |

| 1110  | NE                     | Not equal                      | Z = 0                   |

| 1001  | GE                     | Greater than or equal          | (S XOR V) = 0           |

| 0001  | LT                     | Less than                      | (S XOR V) = 1           |

| 1010  | GT                     | Greater than                   | [Z OR (S XOR V)] = 0    |

| 0010  | LE                     | Less than or equal             | [Z OR (S XOR V)] = 1    |

| 1111  | UGE                    | Unsigned greater than or equal | C = 0                   |

| 0111  | ULT                    | Unsigned less than             | C = 1                   |

| 1011  | UGT                    | Unsigned greater than          | (C = 0  AND  Z = 0) = 1 |

| 0011  | ULE                    | Unsigned less than or equal    | (C OR Z) = 1            |

| 0000  |                        | Never true                     | _                       |

#### Instruction Formats

#### One-Byte Instructions

Two-Byte Instructions

Three-Byte Instructions

# Opcode Map

#### Lower Nibble (Hex)

|                    |                   | 0                                     | 1                                    | 2                                                       | 3                                                     | 4                                                      | 5                                                       | 6                                          | 7                                          | 8                   | 9                   | A                                                                                                          | В                                        | С         | D                              | E          | F                  |

|--------------------|-------------------|---------------------------------------|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|--------------------------------------------|--------------------------------------------|---------------------|---------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------|--------------------------------|------------|--------------------|

|                    | 0                 | 6,5<br>DEC                            | 6,5<br>DEC<br>IR <sub>1</sub>        | 6,5<br>ADD                                              | 6,5<br>ADD<br>r1, lr2                                 | 10, 5<br>ADD<br>R <sub>2</sub> , R <sub>1</sub>        | 10, 5<br>ADD<br>IR 2, R 1                               | 10, 5<br><b>ADD</b><br>R <sub>1</sub> , IM | 10, 5<br>ADD<br>IR <sub>1</sub> , IM       | 6,5<br>LD<br>r1, R2 | 6.5<br>LD<br>r2. R1 | 12-10.5<br>DJNZ<br>11. RA                                                                                  | 12/10,0<br>JR<br>cc, RA                  | 6.5<br>LD | 12/10,0<br><b>JP</b><br>cc, DA | 6,5<br>INC |                    |

|                    | 1                 | 6,5<br>RLC<br>R <sub>1</sub>          | 6,5<br>RLC<br>IR <sub>1</sub>        | 6, 5<br>ADC<br>11, 12                                   | 6, 5<br><b>ADC</b><br>r <sub>1</sub> , l <sub>2</sub> | 10, 5<br>ADC<br>R <sub>2</sub> , R <sub>1</sub>        | 10, 5<br><b>ADC</b><br>IR <sub>2</sub> , R <sub>1</sub> | IO, S<br>ADC<br>R <sub>1</sub> , IM        | 10, 5<br>ADC<br>IR1, IM                    |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

|                    | 2                 | 6, 5<br><b>INC</b><br>R <sub>1</sub>  | 6,5<br>INC<br>IR <sub>1</sub>        | 6, 5<br>SUB<br>11, 12                                   | 6,5<br>SUB<br>r1, lr2                                 | 10, 5<br><b>SUB</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br>SUB<br>IR <sub>2</sub> , R <sub>1</sub>        | 10, 5<br><b>SUB</b><br>R <sub>1</sub> , IM | 10,5<br>SUB<br>IR1,IM                      |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

|                    | 3                 | 8,0<br>JP<br>IRR 1                    | 6, 1<br>SRP<br>IM                    | 6, S<br>SBC<br>11, 12                                   | 6,5<br><b>SBC</b><br>r <sub>1,</sub> lr <sub>2</sub>  | 10, 5<br><b>SBC</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>SBC</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>SBC</b><br>R <sub>1</sub> , IM | 10,5<br>SBC<br>IR <sub>1</sub> ,1M         |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

|                    | 4                 | 8, 5<br><b>DA</b><br>R i              | 8, 5<br><b>DA</b><br>IR <sub>1</sub> | 6, 5<br>OR                                              | 6,5<br>OR<br>r <sub>1</sub> , [r <sub>2</sub>         | 10, 5<br>OR<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br><b>OR</b><br>IR <sub>2</sub> , R <sub>1</sub>  | 10, 5<br>OR<br>R1, IM                      | 10, 5<br>OR<br>IR <sub>1</sub> , IM        |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

|                    | 5                 | 10, 5<br><b>POP</b><br>R <sub>1</sub> | 10, 5<br><b>POP</b><br>IR 1          | 6, 5<br>AND<br>11, 12                                   | 6,5<br>AND<br>r1,1r2                                  | 10, 5<br>AND<br>R <sub>2</sub> , R <sub>1</sub>        | 10, 5<br><b>AND</b><br>IR <sub>2</sub> , R <sub>1</sub> | 10, 5<br>AND<br>R1, IM                     | 10,5<br>AND<br>IR1,IM                      |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

| Hex)               | 6                 | 6, 5<br>COM<br>R <sub>1</sub>         | 6,5<br>COM<br>IR <sub>1</sub>        | 6, 5<br>TCM<br>71, 72                                   | 6,5<br>TCM<br>r1, lr2                                 | 10, 5<br>TCM<br>R <sub>2</sub> , R <sub>1</sub>        | 10,5<br>TCM<br>IR <sub>2</sub> , R <sub>1</sub>         | 10, 5<br>TCM<br>R <sub>1</sub> , IM        | 10,5<br>TCM<br>IR1,IM                      |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

| Upper Nibble (Hex) | 7                 | 10/12, 1<br>PUSH<br>R <sub>2</sub>    | 12/14, 1<br>PUSH<br>IR <sub>2</sub>  | 6, 5<br><b>TM</b><br>r1, r2                             | 6, 5<br><b>TM</b><br>r1, lr2                          | 10, S<br>TM<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br>TM<br>IR <sub>2</sub> , R <sub>1</sub>         | 10, 5<br><b>TM</b><br>R <sub>1</sub> , IM  | 10,5<br>TM<br>IR 1, IM                     |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

| Upper I            | 8                 | 10,5<br>DECW<br>RR,                   | 10, 5<br>DECW<br>IR <sub>1</sub>     | 12,0<br>LDE<br>11,1112                                  | 18, 0<br><b>LDEI</b><br>Ir 1, Irr2                    |                                                        |                                                         |                                            |                                            |                     |                     |                                                                                                            |                                          |           |                                |            | 6.1<br>DI          |

|                    | 9                 | 6, 5<br>RL<br>R <sub>1</sub>          | 6,5<br>RL<br>IR;                     | 12,0<br>LDE<br>12, lrt1                                 | 18.0<br><b>LDEI</b><br>Ir2, Irr1                      |                                                        |                                                         |                                            |                                            |                     |                     |                                                                                                            |                                          |           |                                |            | 6, 1<br>EI         |

|                    | A                 | 10,5<br>INCW<br>RR <sub>1</sub>       | 10,5<br>INCW<br>IR <sub>1</sub>      | 6, 5<br><b>CP</b><br>11, 12                             | 6, 5<br><b>CP</b><br>r <sub>1</sub> , lr <sub>2</sub> | 10, 5<br>CP<br>R <sub>2</sub> , R <sub>1</sub>         | 10,5<br>CP<br>IR <sub>2</sub> , R <sub>1</sub>          | 10, 5<br><b>CP</b><br>R <sub>1</sub> , IM  | 10.5<br>CP<br>IR <sub>1</sub> , IM         |                     |                     |                                                                                                            |                                          |           |                                |            | 14,0<br>RET        |

|                    | В                 | 6,5<br>CLR<br>R <sub>1</sub>          | 6,5<br>CLR<br>IR <sub>1</sub>        | 6, S<br><b>XOR</b><br>11, 12                            | 6,5<br>XOR<br>r <sub>1</sub> , lr <sub>2</sub>        | 10, S<br><b>XOR</b><br>R <sub>2</sub> , R <sub>1</sub> | 10, 5<br><b>XOR</b><br>IR 2, R 1                        | 10, 5<br><b>XOR</b><br>R <sub>1</sub> , IM | 10,5<br>XOR<br>IR <sub>1</sub> , IM        |                     |                     |                                                                                                            |                                          |           |                                |            | 16,0<br>IRET       |

|                    | С                 | 6,5<br>RRC<br>R <sub>1</sub>          | 6,5<br>RRC<br>IR <sub>1</sub>        | 12,0<br><b>LDC</b><br>r <sub>1</sub> , lrr <sub>2</sub> | 18,0<br>LDCI<br>Ir1, Irr2                             |                                                        |                                                         |                                            | 10,5<br><b>LD</b><br>r1, x, R <sub>2</sub> |                     |                     |                                                                                                            |                                          |           |                                |            | 6,5<br>RCF         |

|                    | D                 | 6,5<br><b>SRA</b><br>R <sub>1</sub>   | 6,5<br>SRA<br>IR <sub>1</sub>        | 12,0<br>LDC<br>12, ltr1                                 | 18,0<br>LDCI<br>lt2, ltt1                             | 20,0<br>CALL*<br>IRR1                                  |                                                         | 20,0<br>CALL<br>DA                         | 10, 5<br>LD<br>12, x, R1                   |                     | 1                   |                                                                                                            |                                          |           |                                |            | 6, 5<br><b>SCF</b> |

|                    | E                 | 6,5<br>RR<br>Rı                       | 6,5<br>RR<br>IR <sub>1</sub>         |                                                         | 6, 5<br>LD<br>r1, lr2                                 | 10, 5<br>LD<br>R <sub>2</sub> , R <sub>1</sub>         | 10, 5<br>LD<br>IR <sub>2</sub> , R <sub>1</sub>         | 10,5<br>LD<br>R <sub>1</sub> ,1M           | 10, 5<br><b>LD</b><br>IR <sub>1</sub> , IM |                     |                     |                                                                                                            |                                          |           |                                |            | 6,5<br>CCF         |

|                    | F                 | 6,7<br>SWAP<br>R <sub>1</sub>         | 6,7<br><b>SWAP</b><br>IR1            |                                                         | 6, 5<br>LD<br>Ir 1, r2                                |                                                        | 10.5<br>LD<br>R <sub>2</sub> , IR <sub>1</sub>          |                                            |                                            | +                   |                     |                                                                                                            | +                                        |           |                                | +          | 6, 0<br>NOP        |

|                    | es per<br>ruction |                                       |                                      | 2                                                       | ب                                                     |                                                        |                                                         | 3                                          | _                                          |                     |                     | 2                                                                                                          |                                          |           | 3                              |            | 1                  |

|                    |                   |                                       |                                      |                                                         | Opcod<br>Nibble                                       | •                                                      |                                                         |                                            |                                            |                     |                     |                                                                                                            |                                          |           |                                |            |                    |

|                    |                   | c                                     |                                      | cution<br>Cycles                                        | 10,5<br>CP<br>R <sub>2</sub> , R <sub>1</sub>         | Cyc                                                    | eline<br>cles                                           |                                            |                                            |                     |                     | Legend: R = 8-Bit r = 4-Bit R <sub>1</sub> or r <sub>1</sub> = R <sub>2</sub> or r <sub>2</sub> = Sequence | Address<br>Address<br>Dst Add<br>Src Add | ress      |                                |            |                    |

|                    |                   |                                       | Ор                                   | First erand                                             |                                                       |                                                        | ond<br>erand                                            |                                            |                                            |                     |                     |                                                                                                            |                                          |           | Second C<br>re not def         | •          |                    |

<sup>\*2-</sup>byte instruction; fetch cycle appears as a 3-byte instruction.

# Instruction Summary

| Instruction                                           | Addr Mode         |                      |             | Instruction                                            | Addr              | Mode               | Opcode                      | Flags Affected |  |

|-------------------------------------------------------|-------------------|----------------------|-------------|--------------------------------------------------------|-------------------|--------------------|-----------------------------|----------------|--|

| and Operation                                         | dst src           | Byte<br>(Hex)        | CZSVDH      | and Operation                                          | dst               | src                | Byte<br>(Hex)               | CZSVDH         |  |

| ADC dst,src<br>dst - dst + src + C                    | (Note 1)          | 10                   | * * * * 0 * | LD dst,src<br>dst - src                                | r<br>r            | IM<br>R            | rC<br>r8                    |                |  |

| ADD dst,src<br>dst - dst + src                        | (Note 1)          | 0□                   | * * * * 0 * |                                                        | R                 | r<br>X             | r9<br>r = 0- <b>F</b><br>C7 |                |  |

| AND dst,src<br>dst - dst AND src                      | (Note 1)          | 5□                   | - * * 0     |                                                        | X                 | r<br>Ir            | D7<br>E3                    |                |  |

| CALL dst<br>SP - SP - 2<br>@SP - PC; PC - d           | DA<br>IRR<br>Ist  | D6<br>D4             |             |                                                        | Ir<br>R<br>R<br>R | r<br>R<br>IR<br>IM | F3<br>E4<br>E5<br>E6        |                |  |

| CCF<br>C - NOT C                                      |                   | EF                   | *           |                                                        | IR<br>IR          | IM<br>R            | E7<br>F5                    |                |  |

| CLR dst<br>dst - 0                                    | R<br>IR           | B0<br>B1             |             | LDC dst,src<br>dst - src                               | r<br>Irr          | Irr<br>r           | C2<br>D2                    |                |  |

| COM dst<br>dst - NOT dst                              | R<br>IR           | 60<br>61             | - * * 0     | <b>LDCI</b> dst,src<br>dst - src<br>r - r + 1; rr - rr | Ir<br>Irr<br>+ 1  | Irr<br>Ir          | C3<br>D3                    |                |  |

| CP dst,src<br>dst - src                               | (Note 1)          | A□                   | * * * *     | LDE dst,src<br>dst - src                               | r<br>Irr          | Irr<br>r           | 82<br>92                    |                |  |

| DA dst dst - DA dst  DEC dst                          | R<br>IR<br>R      | 40<br>41<br>00       | * * * X     | LDEI dst,src<br>dst - src                              | Ir<br>Irr         | Irr<br>Ir          | 83<br>93                    |                |  |

| dst ← dst - 1                                         | IR                | 01                   | - * * *     | $\frac{r-r+1; rr-rr}{NOP}$                             | + 1               |                    | FF                          |                |  |

| DECW dst<br>dst - dst - l                             | RR<br>IR          | 80<br>81             | - * * *     | OR dst,src<br>dst - dst OR src                         | (Not              | e 1)               | 40                          | - • • 0        |  |

| <b>DI</b><br>IMR (7) + 0                              |                   | 8F                   |             | POP dst<br>dst - @SP                                   | R<br>IR           |                    | 50<br>51                    |                |  |

| <b>DJNZ</b> $r,dst$ $r \leftarrow r - 1$              | RA                | rA $r = 0-F$         |             | SP ← SP + 1  PUSH src                                  |                   | R                  | 70                          |                |  |

| if r ≠ 0<br>PC ← PC + dst<br>Range: +127, -128        |                   |                      |             | SP - SP - 1; @ SP<br>RCF                               | - src             | IR                 | 71°<br>CF                   | 0              |  |

| EI                                                    |                   | 9F                   |             | <u>C</u> - 0                                           |                   |                    |                             | 0              |  |

| IMR (7) ← 1 INC dst                                   | r                 | гE                   | - * * *     | <b>RET</b><br>PC ← @ SP; SP ← S                        | SP + 2            |                    | AF                          |                |  |

| dst - dst + 1                                         | R<br>IR           | r = 0-F<br>20<br>21  |             | RL dst                                                 | J R<br>IR         |                    | 90<br>91                    | * * * *        |  |

| INCW dst<br>dst - dst + 1                             | RR<br>IR          | A0<br>A1             | - * * *     | RLC dst                                                | I R<br>IR         |                    | 10<br>11                    | * * * *        |  |

| IRET                                                  |                   | BF                   | * * * * * * | RR dst                                                 | P R<br>IR         |                    | E0<br>E1                    | * * * * = =    |  |

| FLAGS - @ SP; SF<br>PC - @ SP; SP - S                 |                   | 7) - 1               |             | RRC dst                                                | R<br>IR           |                    | C0<br>C1                    | * * * * * -    |  |

| JP cc,dst<br>if cc is true<br>PC - dst                | D <b>A</b><br>IRR | cD<br>c=0-F<br>30    |             | SBC dst,src<br>dst - dst - src - C                     | (Note             | e l)               | 3□                          | * * * * 1 *    |  |

| JR cc,dst                                             | RA                | сВ                   |             | <b>SCF</b> C - 1                                       | -                 |                    | DF                          | 1              |  |

| if cc is true,<br>PC - PC + dst<br>Range: + 127, -128 |                   | $c = 0 - \mathbf{F}$ |             | SRA dst                                                | ⊋ R<br>IR         |                    | D0<br>D1                    | * * * 0        |  |

#### Instruction Summary (Continued)

| Instruction                      | Addr      | Mode | Opcode        | Flags Affected |  |  |  |  |  |

|----------------------------------|-----------|------|---------------|----------------|--|--|--|--|--|

| and Operation                    | dst       | src  | Byte<br>(Hex) | CZSVDH         |  |  |  |  |  |

| SRP src<br>RP - src              |           | Im   | 31            |                |  |  |  |  |  |

| SUB dst,src<br>dst - dst - src   | (Note     | el)  | 2[]           | • • • • 1 •    |  |  |  |  |  |

| SWAP det                         | ∃ R<br>IR |      | F0<br>F1      | X • • X        |  |  |  |  |  |

| TCM dst,src<br>(NOT dst) AND src | (Note     | el)  | 6□            | - • • 0        |  |  |  |  |  |

| TM dst,src<br>dst AND src        | (Note     | e l) | 7[]           | - • • 0        |  |  |  |  |  |

| XOR dst,src<br>dst – dst XOR src | (Note     | e l) | BC            | - • • 0        |  |  |  |  |  |

#### Note 1

These instructions have an identical set of addressing modes, which are encoded for brevity. The first opcode nibble is found in the instruction set table above. The second nibble is expressed symbolically by a  $\mathbb T$  in this table, and its value is found in the following table to the left of the applicable addressing mode pair.

For example, to determine the opcode of an ADC instruction using the addressing modes r (destination) and Ir (source) is 13.

| Āddr  | Mode | Lower         |  |

|-------|------|---------------|--|

| dst   | src  | Opcode Nibble |  |

| <br>r | r    |               |  |

| г     | lr   | (3)           |  |

| R     | R    | <u>(4)</u>    |  |

| R     | IR   | 5             |  |

| R     | IM   | 6             |  |

| IR    | IM   | Ī             |  |

#### Registers

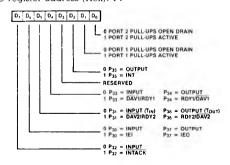

#### R248 P1M Port 1 Mode Register

UPC register address (Hex): F8

#### R246 P2M Port 2 Mode Register

UPC register address (Hex): F6

#### R247 P3M Port 3 Mode Register

UPC register address (Hex): F7

Figure 12. Port Mode Registers

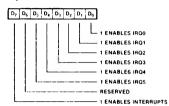

#### R251 IMR Interrupt Mask Register

UPC register address (Hex): FB

#### R250 IRQ Interrupt Request Register

UPC register address (Hex): FA

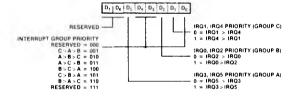

#### R249 IPR Interrupt Priority Register

UPC register address (Hex): F9 (Write Only)

Figure 13. Interrupt Control Registers

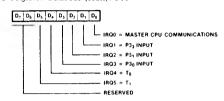

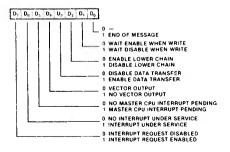

# R254 MIC Master CPU Interrupt Control Register

UPC register address (Hex): FE

# R240 MIV Master CPU Interrupt Vector Register

UPC register address (Hex): F0

Figure 14. Master CPU Interrupt Registers

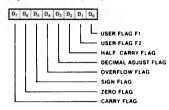

#### R252 FLAGS Flag Register

UPC register address (Hex): FC

# R253 RP Register Pointer

UPC register address (Hex): FD

#### R255 SP Stack Pointer

UPC register address (Hex): FF

Figure 15. UPC Control Registers

#### R0 DTC R4 LC **Data Transfer Control Register** Limit Count Register UPC register address (Hex): 00 UPC register address (Hex): 04 D, D, D, D, D, D, D, D, D, D6 D5 D4 D3 D2 D, D0 LIMIT COUNT VALUE (RANGE: 0-255 DECIMAL 00-FF HEX) (EOM) END OF MESSAGE NO TRANSFER ERROR TRANSFER ERROR R5 DIND NO LIMIT ERROR LIMIT ERROR Data Indirection Register (EDX) UPC register address (Hex): 05 DISABLE DATA TRANSFER D, D6 D5 D4 D3 D2 D1 D0 I/O REGISTER POINTER INDIRECTION ADDRESS (Do = LSB)

Figure 16. Master CPU-UPC Data Transfer Registers

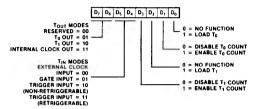

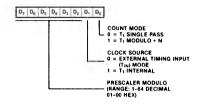

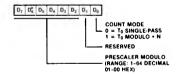

#### R241 TMR Timer Mode Register

UPC register address (Hex): F1

#### R243 PRE1 Prescaler 1 Register

UPC register address (Hex): F3

# R242 Tl Counter/Timer 1 Register

UPC register address (Hex): F2

#### R244 T0 Counter/Timer 0 Register

UPC register address (Hex): F4

#### R245 PRE0 Prescaler 0 Register

UPC register address (Hex): F5

Figure 17. UPC Counter/Timer Registers

| Control Register                                            | D <sub>7</sub> | D <sub>6</sub> | $D_5$ | $D_4$   | $D_3$ | D <sub>2</sub> | Dı | D <sub>0</sub> | Comments                                                                                                                                                                                             |

|-------------------------------------------------------------|----------------|----------------|-------|---------|-------|----------------|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 <sub>H</sub><br>Data Transfer Control Register           | Х              | Х              | Х     | Х       | 0     | 0              | 0  | 0              | Disable data transfer<br>from master CPU                                                                                                                                                             |

| 04 <sub>H</sub><br>Limit Count Register                     |                |                |       | Not De  | fined |                |    |                |                                                                                                                                                                                                      |

| 05 <sub>H</sub><br>Data Indirection Register                |                |                |       | Not De  | fined |                |    |                |                                                                                                                                                                                                      |

| FO <sub>H</sub><br>Interrupt Vector Register                |                |                |       | Not De  | fined |                |    |                |                                                                                                                                                                                                      |

| Fl <sub>H</sub><br>Timer Mode                               | 0              | 0              | 0     | 0       | 0     | 0              | 0  | 0              | Stops T0 and T1                                                                                                                                                                                      |

| F2 <sub>H</sub><br>T0 Register                              |                |                |       | Not De  | fined |                |    |                |                                                                                                                                                                                                      |

| F3 <sub>H</sub><br>T0 Prescaler                             | Х              | Х              | Х     | X       | Х     | Х              | 0  | 0              | Single-Pass mode                                                                                                                                                                                     |

| F4 <sub>H</sub><br>T1 Register                              |                |                |       | Not De  | ined  |                |    |                |                                                                                                                                                                                                      |

| F5 <sub>H</sub><br>T1 Prescaler                             | Х              | Х              | Х     | Х       | Х     | Х              | 0  | 0              | Single-Pass mode<br>External clock source                                                                                                                                                            |

| F6 <sub>H</sub><br>Port 2 Mode                              | 1              | 1              | 1     | 1       | l     | l              | l  | 1              | Port 2 lines defined as inputs                                                                                                                                                                       |

| F7 <sub>H</sub><br>Port 3 Mode                              | 0              | 0              | 0     | 0       | Х     | 1              | 0  | 0              | Port 1, 2 open drain;<br>P3 <sub>5</sub> = INT; P3 <sub>0</sub> , P3 <sub>1</sub> , P3<br>P3 <sub>3</sub> defined as input; P3 <sub>4</sub> ,<br>P3 <sub>6</sub> , P3 <sub>7</sub> defined as output |

| F8 <sub>H</sub><br>Port 1 Mode                              | 1              | 1              | 1     | l       | 1     | 1              | 1  | 1              | Port 1 lines defined as inputs                                                                                                                                                                       |

| F9 <sub>H</sub><br>Interrupt Priority                       |                |                | 1     | Not Def | ined  |                |    |                |                                                                                                                                                                                                      |

| FA <sub>H</sub><br>Interrupt Request                        | X              | Х              | 0     | 0       | 0     | 0              | 0  | 0              | Reset Interrupt Request                                                                                                                                                                              |

| FB <sub>H</sub><br>Interrupt Mask                           | 0              | Х              | Х     | Х       | Х     | Х              | Х  | Х              | Interrupts disabled                                                                                                                                                                                  |

| FC <sub>H</sub><br>Flag Register                            |                |                | 1     | Not Def | ined  |                |    |                |                                                                                                                                                                                                      |

| FD <sub>H</sub><br>Register Pointer                         |                |                | 1     | Not Def | ined  |                |    |                |                                                                                                                                                                                                      |

| FE <sub>H</sub><br>Master CPU Interrupt<br>Control Register | 0              | 0              | 0     | 0       | 0     | 0              | 0  | 0              | Master CPU interrupt dis-<br>abled; wait enable when<br>write; lower chain enabled                                                                                                                   |

| FF <sub>H</sub><br>Stack Pointer                            |                |                | N     | Not Def | ined  |                |    |                |                                                                                                                                                                                                      |

#### **Absolute Maximum Rating**

Voltages on all pins (except  $V_{BB}$ ) with respect to GND......0.5 V to +7.0 V Operating Ambient Temperature.....0°C to +70°C Storage Temperature.....65°C to +150°C

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

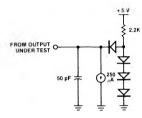

#### **Standard Test Conditions**

The characteristics below apply for the following standard test conditions, unless otherwise noted. All voltages are referenced to GND. Positive current flows into the reference pin. Standard conditions are as follows:

■

$$+4.75 \text{ V} \le \text{V}_{CC} \le +5.25 \text{ V}$$

$$\blacksquare V_{SS} = GND = 0 V$$

$$\bullet$$

0°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C

Figure 18. Test Load 1

Figure 19. Test Load 2

#### DC Characteristics

| Syml                | pol Parameter                  | Min  | Max             | Unit    | Condition                          | Notes |

|---------------------|--------------------------------|------|-----------------|---------|------------------------------------|-------|

| $\overline{v_{CH}}$ | Clock Input High Voltage       | 2.4  | V <sub>CC</sub> | V       |                                    |       |

| $V_{CL}$            | Clock Input Low Voltage        | -0.3 | 0.8             | V       |                                    |       |

| $V_{IH}$            | Input High Voltage             | 2.0  | $v_{cc}$        | V       |                                    |       |

| $V_{\rm IL}$        | Input Low Voltage              | -0.3 | 0.8             | V       |                                    |       |

| $V_{OH}$            | Output High Voltage            | 2.4  |                 | V       | $I_{OH} = -250 \mu\text{A}$        | 1     |

| $V_{OL}$            | Output Low Voltage             |      | 0.4             | V       | $I_{OL} = +2.0 \text{ mA}$         | l     |

| $I_{IL}$            | Input Leakage                  | -10  | 10              | $\mu$ A | $0 \le V_{IN} \le +5.25 \text{ V}$ |       |

| $I_{OL}$            | Output Leakage                 | -10  | 10              | $\mu$ A | $0 \le V_{1N} \le +5.25 \text{ V}$ |       |

| $I_{\rm CC}$        | V <sub>CC</sub> Supply Current |      | 180             | mÅ      |                                    |       |

<sup>1.</sup> For A<sub>0</sub>-A<sub>11</sub> and D<sub>0</sub>-D<sub>7</sub>,  $\overline{\text{MDS}}$ ,  $\overline{\text{SYNC}}$ ,  $\overline{\text{MAS}}$ , and  $\overline{\text{MR}}/\overline{\text{W}}/\text{IACK}$  on the 64-pin versions.  $I_{OH}=100~\mu$  A and  $I_{OL}=1.0~\text{mA}$ .

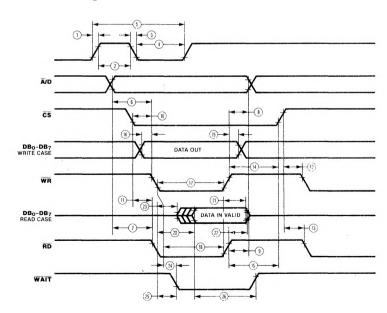

# Master CPU Interface Timing

| Numbe | r Symbol      | Parameter                                        | Min (ns) | Max (ns) | Notes*   |

|-------|---------------|--------------------------------------------------|----------|----------|----------|

| 1     | TrC           | Clock Rise Time                                  |          | 20       |          |

| 2     | TwCh          | Clock High Width                                 | 105      | 1855     |          |

| 3     | TfC           | Clock Fall Time                                  |          | 20       |          |

| 4     | TwCl          | Clock Low Width                                  | 105      | 1855     |          |

| 5     | TpC           | Clock Period                                     | 250      | 2000     |          |

| 6 —   | - TsA/D(WR) - | — A/D to WR   Setup Time                         | 80 —     | -        |          |

| 7     | TsA/D(RD)     | $\overline{A}/D$ to $\overline{RD}$   Setup Time | 80       |          |          |

| 8     | ThA/D(WR)     | A/D to WR † Hold Time                            | 30       |          |          |

| 9     | ThA/D(RD)     | $\overline{A}/D$ to $\overline{RD}$ † Hold Time  | 30       |          |          |

| 10    | TsCSf(WR)     | CS ↓ toWR ↓ SetupTime                            | 0        |          |          |

| 11 —  | - TsCSf(RD) - | — CS I to RD I Setup Time —                      | 0-       |          |          |

| 12    | TsCSr(WR)     | CS to WR   Setup Time                            | 60       |          |          |

| 13    | TsCSr(RD)     | CS 1 to RD ↓ Setup Time                          | 60       |          |          |

| 14    | ThCS(WR)      | CS to WR ↓ Hold Time                             | 0        |          |          |

| 15    | ThCS(RD)      | CS to RD   Hold Time                             | 0        |          |          |

| 16 —  | - TsDI(WR)    | - Data in to WR   Setup Time                     | 0        | ····     |          |

| 17    | Tw(WR)        | WR Low Width                                     | 390      |          |          |

| 18    | Tw(RD)        | RD Low Width                                     | 390      |          |          |

| 19    | ThWR(DI)      | Data in to WR   Hold Time                        | 0        |          |          |

| 20    | TdRD(DI)      | Data Valid from RD   Delay                       |          |          | 1        |

| 21 —  | - ThRD(DI) -  | — Data Valid to RD   Hold Time ————              | 0        |          | <u>.</u> |

| 22    | $TdRD(DI_Z)$  | Data Bus Float Delay from RD 1                   |          | 70       |          |

| 23    | $TdRD(DB_A)$  | RD I to Read Data Active Delay                   | 0        |          |          |

| 24    | TdWR(W)       | WR ↓ to WAIT ↓ Delay                             |          | 150      |          |

| 25    | TdRD(W)       | RD   to WAIT   Delay                             |          | 150      |          |

| 26    | TdDI(W)       | Data Valid to WAIT   Delay                       | 0        |          |          |

This parameter is dependent on the state of the UPC at the time of master CPU access.

<sup>3.</sup> The timing characteristics given reference 2.0 V as High and 0.8 V as Low.

<sup>4.</sup> All output ac parameters use test load 1.\*Timings are preliminary and subject to change.

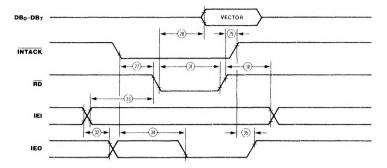

#### **Interrupt Acknowledge Transactions**

| Numbe | r Symbol                 | Parameter                   | Min (ns) | Max (ns) | Notes* |

|-------|--------------------------|-----------------------------|----------|----------|--------|

| 27    | TsACK(RD)                | INTACK I to RD I Setup Time | 90       |          | 2      |

| 28    | TdRD(DI)                 | RD   to Vector Valid Delay  |          | 255      |        |

| 29    | ThRD(ACK)                | RD † to INTACK † Hold Time  | 0        |          |        |

| 30    | ThIEI(RD)                | IEI to RD   Hold Time       | 100      |          |        |

| 31 —  | TwRDI ———                | RD (Acknowledge) Low Width  | 255 —    |          |        |

| 32    | TdIEI(IEO)               | IEI to IEO Delay            |          | 120      |        |

| 33    | TsIEI(RD)                | IEI to RD   Setup Time      | 150      |          |        |

| 34    | TdACK <sub>f</sub> (IEO) | INTACK   to IEO   Delay     |          | 250      |        |

| 35    | TdACK <sub>r</sub> (IEO) | INTACK 1 to IEO 1 Delay     |          | 250      |        |

|       | •                        |                             |          |          |        |

#### NOTES:

- 2. In case where daisy chain is not used.

3. The timing characteristics given reference 2.0 V as High and 0.8 V as Low.

- 4. All output ac parameters use test load 1. \*Timings are preliminary and subject to change.

# Master CPU Interface Timing

# Interrupt Acknowledge Timig

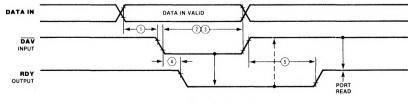

#### Handshake Timing

| Numbe | er Symbol | Parameter                                  | Min (ns) | Max (ns) | Notes*     |

|-------|-----------|--------------------------------------------|----------|----------|------------|

| l     | TsDI(DA)  | Data In Setup Time                         | 0        |          |            |

| 2     | ThDA(DI)  | Data In Hold Time                          | 230      |          |            |

| 3     | TwDA      | Data Available Width                       | 175      |          | 1,2        |

| 4     | TdDAL(RY) | Data Available Low to Ready<br>Delay Time  | 20<br>0  | 175      | 1,2<br>2,3 |