# DJ-191

## **Service Manual**

### CONTENTS

|                                    | 2  |

|------------------------------------|----|

|                                    |    |

| <b>•</b> SEMICONDUCTOR DATA ······ | 9  |

|                                    | 15 |

| PARTS LIST                         |    |

|                                    | 21 |

|                                    | 26 |

|                                    | 41 |

|                                    |    |

### SPECIFICATIONS

FrequencyCoverage DJ-191T (US Amateur version) **IX** 144000~147995MHz 135000 .173-995MHz DJ-191E (European Anateur version) 144000 9911z 144 000 ~ 145 995MHz 149 155000MHz 135 000 173-995MHz DJ-191TA1 (Commercial versionVHFL) 135 000 DJ-191TA2(Commercial version VHFH) 150 000 173995Mz 135 000 1.73-995MHz 5 10 125 15 20 25,30kHz steps Channel Step. 40 Ch annes + C llaCh annte Memory Channels: emory Antenna Impedance:  $50\Omega$  unbalanced **Frequency Stability:**  $\pm 5 \text{ ppm}$ Microphone Input Impedance:  $2k\Omega$  nominal. Signal Type: F3E (FM) **Offset Range:**  $0 \sim 99.995 MHz$ **Deviation:**  $\pm$  5kHz max. TX Output (supply voltage): 1.5W (4.8V) / 3.5W (7.2V) / 5W (9.6~13.8V) **RX Sensitivity:** 12dB SINAD better than  $-16dB_{\mu}$ **RX Selectivity:** -6dB/ $\pm$ 12kHz I.F.: (1st) 21.25MHz / (2nd) 450kHz 4.8~13.8V DC (4.8V DC standard) Power Supply Requirements: Transmitting: Approx. 1.2 Amp. in High Power **Current Consumption** at 13.8V DC: Setting Receiving: Squelched Approx. 24mA (BS on)  $-10 \sim +60^{\circ}$ C.  $14 \sim 140^{\circ}$ F **Operating Temperature:** 57(W) × 151(H) × 28(D) mm Dimensions: (with EBP-37N without projections)  $2^{1}/_{4}(W) \times 6(H) \times 1^{1}/_{16}(D)$  inches Weight: Approx. 300g DTMF: 16 Button Keypad, encoder/decoder installed Subaudible Tones (CTCSS): Encoder installed (50 tones)

### **CIRCUIT DESCRIPTION**

### 1) Receiver System

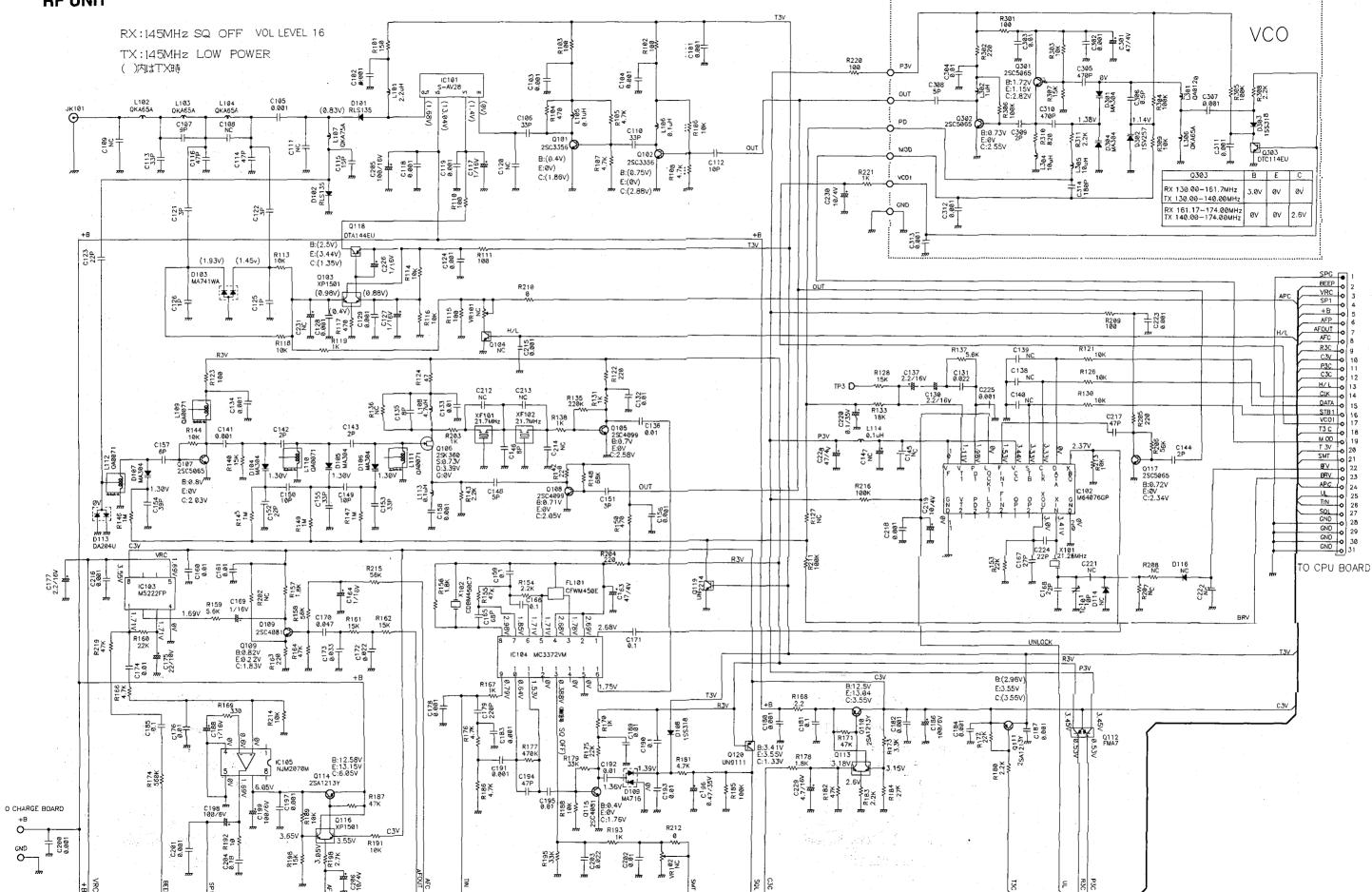

The receiver system is a double superheterodyne system with a 21.7 MHz first IF and a 450 kHz second IF.

### 1. Front End

The received signal at any frequency in the 130.00- to 173.995-MHz range is passed through the low-pass filter (L102, L103, L104, C113, C107, C116, and C114) and tuning circuit (L112 and D107), and amplified by the RF amplifier (Q107). The signal from Q107 is then passed through the tuning circuit (L109, L110, L111, and varicaps D104, D105 and D106) and converted into 21.7 MHz by the mixer (Q106). The tuning circuit, which consists of L112, L109, varicaps D107 and D104, L110, L111, varicaps D105 and D106, is controlled by the tracking voltage from the CPU so that it is optimized for the reception frequency. The local signal from the VCO is passed through the buffer (Q108), and supplied to the source of the mixer (Q106). The radio uses the lower side of the superheterodyne system.

### 2. IF Circuit

The mixer mixes the received signal with the local signal to obtain the sum of and difference between them. The crystal filter (XF101, XF102) selects 21.7 MHz frequency from the results and eliminates the signals of the unwanted frequencies. The first IF amplifier (Q105) then amplifies the signal of the selected frequency.

### 3. Demodulator Circuit

After the signal is amplified by the first IF amplifier (Q105), it is input to pin 16 of the demodulator IC (IC104). The second local signal of 21.25 MHz (shared with PLL IC reference oscillation), which is oscillated by the internal oscillation circuit in IC102 and crystal (X101), is input through pin 1 of IC104. Then, these two signals are mixed by the internal mixer in IC104 and the result is converted into the second IF signal with a frequency of 450 kHz. The second IF signal is output from pin 3 of IC104 to the ceramic filter (FL101), where the unwanted frequency band of that signal is eliminated, and the resulting signal is sent back to the IC104 through pins 5 and 7.

The second IF signal input via pin 7 is demodulated by the internal limiter amplifier and quadrature detection circuit in IC104, and output as an audio signal through pin 9.

### 4. Audio Circuit

The audio signal from pin 9 of IC104 is compensated to the audio frequency characteristics in the de-emphasis circuit (R162, R161, C172, C173) and amplified by the AF amplifier (Q109). The signal is then input to pin 2 of the electronic volume (IC103) for volume adjustment, and output from pin 1. The adjusted signal is sent to the audio power amplifier (IC105) through pin 2 to drive the speaker.

### 5. Squelch Circuit

Part of the audio signal from pin 9 of IC104 is amplified by the noise filter amplifier consisting of R176, R186, R177, C179, C183, C191, and C194, and the internal noise amplifier in IC104. The desired noise of the signal is output through pin 11 of IC104, to be further amplified by the noise amplifier (Q115). The amplified noise signal is rectified by voltage doubler D109 and input to pin 4 of CPU (IC5).

### 2) Transmitter System

### **1. Modulator Circuit**

The audio signal is converted to an electric signal in either the internai or external microphone, and input to the microphone amplifier (IC6). IC6 consists of two operational amplifiers; one amplifier (pins 1, 2, and 3) is composed of pre-emphasis and IDC circuits and the other (pins 5, 6, and 7) is composed of a splatter filter. The maximum frequency deviation is obtained by VR2 and input to the cathode of the varicap of the VCO, to change the electric capacity in the oscillation circuit. This produces the frequency modulation.

### 2. Power Amplifier Circuit

The transmitted signal is oscillated by the VCO, amplified by the pre-drive amplifier (Q102) and drive amplifier (Q101), and input to the power module (IC101). The signal is then amplified by the power module (IC101) and led to the antenna switch (D101) and low-pass filter (L102, L103, L104, C113, C107, C116, and C114), where unwanted high harmonic waves are reduced as needed, and the resulting signal is supplied to the antenna.

### 3. APC Circuit

Part of the transmission power from the low-pass filter is detected by D103, converted to DC, and then amplified by a differential amplifier. The output voltage controls the bias voltage from pin 2 of the power module (IC101) to maintain the transmission power constant.

### 3) PLL Synthesizer Circuit 1. PLL The

The dividing ratio is obtained by sending data from the CPU (IC5) to pin 2 and sending clock puises to pin 3 of the PLL IC (IC102). The oscillated signal from the VCO is amplified by the buffer (Q117) and input to pin 6 of IC102. Each programmable divider in IC102 divides the frequency of the input signal by N according to the frequency data, to generate a comparison frequency of 5 or 6.25 kHz.

### 2. Reference Frequency Circuit

The reference frequency appropriate for the channel steps is obtained by dividing the 21.25 MHz reference oscillation (X101) by 4250 or 3400, according to the data from the CPU (IC5). When the resulting frequency is 5 kHz, channel steps of 5, 10, 15, 20, 25, 30, and 50 kHz are used. When it is 6.25 kHz, the 12.5 kHz channel step is used.

- 3. Phase Comparator Circuit The PLL (IC102) uses the reference frequency, 5 or 6.25 kHz. The phase comparator in the IC102 compares the phase of the frequency from the VCO with that of the comparison frequency, 5 or 6.25 kHz, which is obtained by the internal divider in IC102.

- 4. PLL Loop Filter Circuit If a phase difference is found in the phase comparison between the reference frequency and VCO output frequency, the charge pump output (pin 8) of IC102 generates a pulse signal, which is converted to DC voltage by the PLL loop filter and input to the varicap of the VCO unit for oscillation frequency control.

- 5. VCO Circuit A Colpitts oscillation circuit driven by Q301 directly oscillates the desired frequency. The frequency control voltage determined in the CPU (IC5) and PLL circuit is input to the varicaps (D301 and D304). This changes the oscillation frequency, which is amplified by the VCO buffer (Q302) and output from the VCO unit.

#### Note

The oscillation frequency is determined by turning Q301 ON and OFF.

| Displayed frequencies    | Q301 |

|--------------------------|------|

| TX: 130.00 - 139.995 MHz | 055  |

| RX: 130.00 - 161.695 MHz | OFF  |

| TX: 140.00 - 173.995 MHz |      |

| RX: 161.70 - 173.995 MHz | ON   |

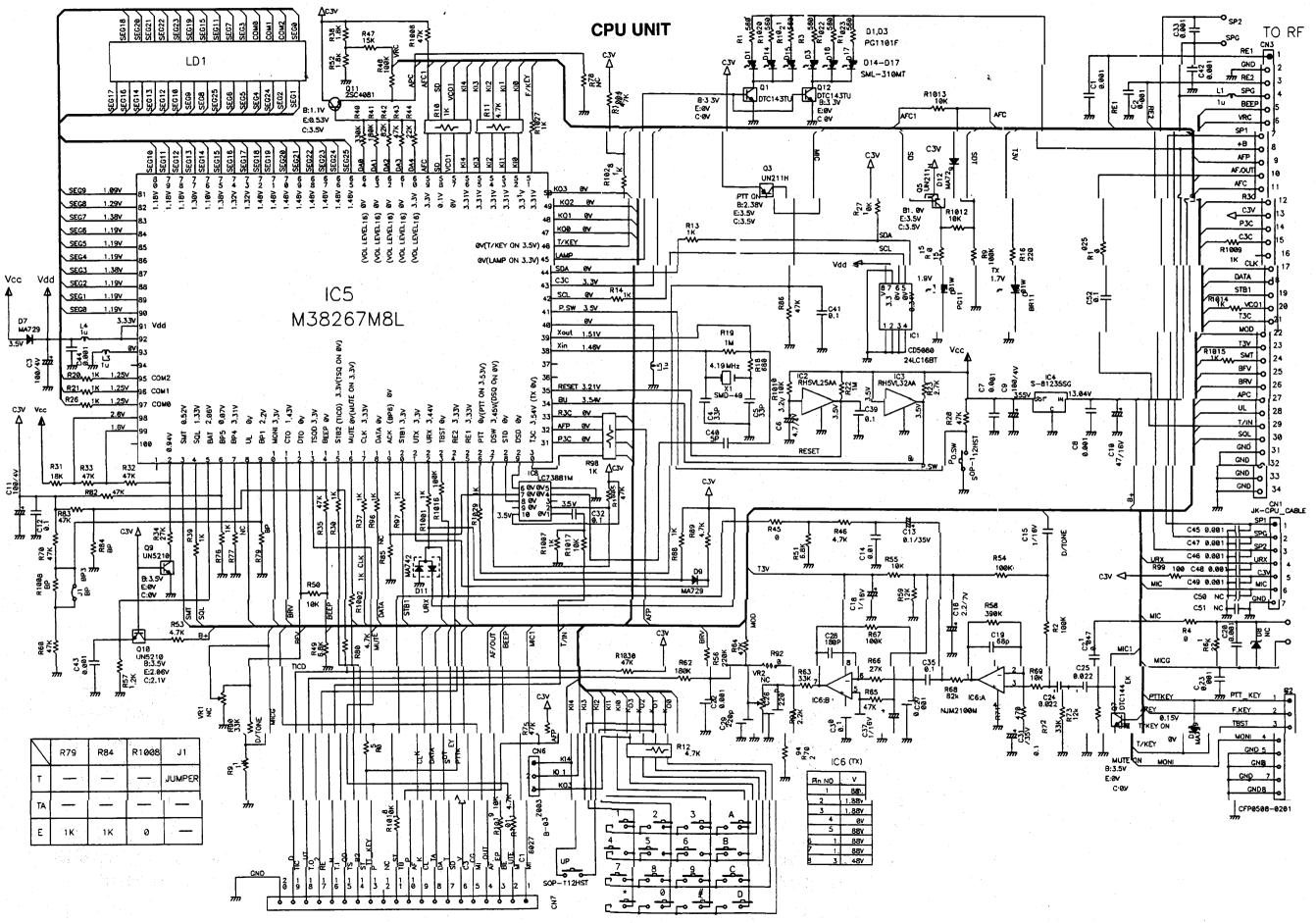

### 4) CPU and Peripheral Circuits

1. LCD Display Circuit

The CPU turns ON the LCD via segment and common terminals with 1/3 the duty and 1/3 the bias, at the frame frequency is 85Hz.

2. Display Lamp Circuit When the LAMP key is pressed, "H" is output from pin 45 of CPU (IC5) to the bases of Q1 and Q12. Q1 and Q12 then turn ON and the LEDs (D1, D3, D14, D15, D16, and D17) light.

### 3. Reset and Backup Circuits

When the power from the DC jack or external battery increases from 0 V to 2.5 or more, "H" level reset signal is output from the reset IC (IC2) to pin 35 of the CPU (IC5), causing the CPU to reset. The reset signal, however, waits at C6 and R1010, and does not enter the CPU until the CPU clock (X1) has stablized. When the external power drops to 3.2 V or below, the output signal from the backup IC (IC3), which has been input to pin 34 of the CPU, changes from "H" to "L" level. The CPU will then be in the backup state.

- 4. S(Signal)Meter Circuit The DC potential of pin 13 of IC104 is input to pin 3 of the CPU (IC5), converted from an analog to a digital signal, and displayed as the S-meter signal on the LCD.

- 5. DTMF Encoder The CPU (IC5) is equipped with an internal DTMF encoder. The DTMF signal is output from pin 12, through R90 and R91 (for level adjustment), and then through the microphone amplifier (IC6), and is sent to the varicap of the VCO for modulation. At the same time, the monitoring tone passes through the AF circuit and is output from the speaker.

- 6. DTMF Decoder Part of the audio signal demodulated by IC104 is input to pin 1 of DTMF IC (IC8). The internal signal judging circuit in IC 8 then checks if the signal is valid or invalid. The judged signal is converted into a 4-bit code and sent to pin 29 of IC5.

- 7. Tone Encoder The CPU (IC5) is equipped with an internal tone encoder. The tone signal (67.0 to 254.1 Hz) is output from pin 11 of the CPU to the varicap of the VCO for modulation.

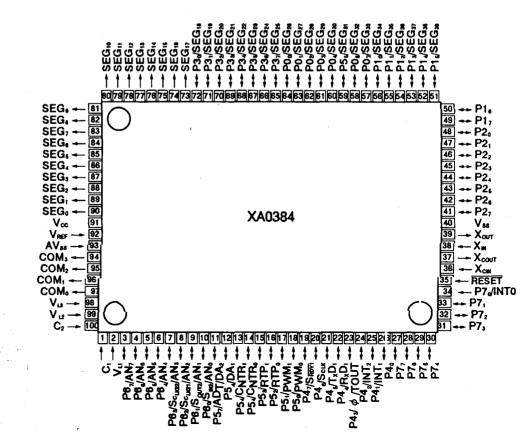

### 5) CPU Terminal Functions: M38267M8L (XA0384)

| No.                  | Pin Name      | Signal | I/O           | Logic               | Description                                                                                         |

|----------------------|---------------|--------|---------------|---------------------|-----------------------------------------------------------------------------------------------------|

| 1                    | C1            | C1     | -             | _                   | -                                                                                                   |

| 2                    | VL1           | VL1    | 1             | A/D                 | LCD power supply                                                                                    |

| 3                    | P67/AN7       | SMT    | 1             | A/D                 | S-meter input                                                                                       |

| 4                    | P66/AN6       | SQL    | t ī           | A/D                 | Noise level input for squelch                                                                       |

| 5                    | P65/AN5       | BAT    | 1             | A/D                 | Low battery detection input                                                                         |

| 6                    | P64/AN4       | BP5    | 1             | A/D                 | Band plan 5                                                                                         |

| 7                    | P63/CLK22/AN3 | BP4    | 1             |                     | Band plan 4                                                                                         |

| 8                    | P62/CLK21/AN2 | UL     | I             | Active high         | PLL unlock signal input                                                                             |

| 9                    | P61/SOUT2/AN1 | BP1,2  |               | A/D                 | Band plans 1 and 2                                                                                  |

| 10                   | P60/SIN2/AN0  | MONI   | 1             | Active low          | Monitor key input                                                                                   |

| 11                   | P57/ADT/DA2   | стоит  | 0             | D/A                 | CTCSS tone output                                                                                   |

| 12                   | P56/AD1       | DTOUT  | <u> </u>      | D/A                 | DTMF output                                                                                         |

| 13                   | P55/CNTR1     | TSQD   |               | Active low          | CTCSS tone detection input/Trunking board detection                                                 |

| 14                   | P54/CNTR0     | BEP    | 0             | Pulse               | Beep tone output/Band plan 3                                                                        |

| 15                   | P53/RTP1      | STB2   | 1/0           | Active low/pulse    | CTCSS unit detection/Strobe signal to CTCSS unit/Strobe signal to trunking board/Audio line control |

| 16                   | P52/RTP0      | MUTE   | 1/0           | Active high         | Microphone mute/Bank change input while trunking                                                    |

| 17                   | P51/PWM1      | CLK    | 0             | Pulse               | Serial clock output for PLL, CTCSS, and trunking board                                              |

| 18                   | P50/PWM0      | DATA   | 0             | Pulse               | Serial data output for PLL, CTCSS, and trunking board                                               |

| 19                   | P47/SRDY1     | ACK    | 1/0           | Pulse               | Clock output for DTMF shift out/Band plan 6                                                         |

| 20                   | P46/SCLK1     | STB1   | 0             | Pulse               | Strobe for PLL IC                                                                                   |

| 21                   | P45/TXD1      | UTX    | 0             | Pulse               | UART data transmission output                                                                       |

| 22                   | P44/RXD1      | URX    | Ĭ             | Pulse               | UART data reception input                                                                           |

| 23                   | P43/ø/TOUT    | TBST   | 0             | Pulse               | Tone burst (1750Hz) output (European version)                                                       |

| 24                   | P42/INT2      | RE2    |               | Active low          |                                                                                                     |

| 25                   | P41/INT1      | RE1    | $\frac{1}{1}$ | Active low          | Rotary encoder input                                                                                |

| 23<br>26             | P40           | ΡΤΤ    |               | Active high         | PTT input                                                                                           |

| 27                   | P77           | DSW    | 0             | Active low          | DTMF IC ON/OFF                                                                                      |

| 28                   | P76           | STD    | 1/0           | Active high         | DTMF signal detection input during reception/Deviation adjustment during transmission               |

| 29                   | P75           | DSD    | 1             | Pulse               | Decoded DTMF serial data input during reception/Deviation adjustment during transmission            |

| 30                   | P74           | T3C    | 0             | Active low          | TX power ON/OFF output                                                                              |

| 31                   | P73           | P3C    | 0             | Active low          | PLL power ON/OFF output                                                                             |

| 32                   | P72           | AFP    | 0             | Active low          | AFAMP power ON/OFF output                                                                           |

| 33                   | P71           | R3C    | 0             | Active low          | RX power ON/OFF output                                                                              |

| 34                   | P70/INTO      | BU     |               | Active low          | Backup signal detection input                                                                       |

| 35                   | RESET         | RST    | 1             | Active low          | Reset input                                                                                         |

| 36                   | XCIN          | XCIN   | -             |                     |                                                                                                     |

| 30                   | XCOUNT        | XCOUT  | -             |                     | _                                                                                                   |

| 37                   | XIN           | XIN    | -             | -                   | -<br>Main clock input                                                                               |

| 30<br>39             | XOUT          | XOUT   | -<br>         | -                   | Main clock input                                                                                    |

|                      | VSS           | GND    | ·· -          | -                   | CPU ground                                                                                          |

| 40<br>41             | VSS<br>P27    | PSW    | -             |                     | Power switch input                                                                                  |

|                      | P27<br>P26    | SCL    | 0             | Active low<br>Pulse | Serial clock for EEPROM                                                                             |

| 42<br>43             | P26<br>P25    | C3C    | 0             | Active high         | C3 power ON/OFF output                                                                              |

| 43                   | P23<br>P24    | SDA    | 0             | Pulse               | Serial data for EEPROM                                                                              |

|                      | P24<br>P23    | LMP    | 0             | Active high         | Lamp ON/OFF                                                                                         |

| 45<br>46             | P23<br>P22    | T/KEY  |               | Active high         | Tone burst/LPTT input                                                                               |

| 46<br>47             | P22<br>P21    | KO0    | 1/0           |                     | Key matrix output/Band plan BP7 input                                                               |

| 48                   | P20           | K01    | 0             | _                   |                                                                                                     |

| 40                   | P17           | K02    | 0             | _                   | Key matrix output                                                                                   |

| <del>4</del> 9<br>50 | P16           | K02    | 0             |                     |                                                                                                     |

| 30                   | FIU           | 1.03   |               |                     |                                                                                                     |

| No.      | Pin Name       | Signal   | I/O | Logic       | Description                                         |

|----------|----------------|----------|-----|-------------|-----------------------------------------------------|

| 51       | P15/SEG39      | F/KEY    |     | Active low  | Function key input                                  |

| 52       | P14/SEG38      | K10      | 1   | -           |                                                     |

| 53       | P13/SEG37      | K11      | 1   | -           | 1                                                   |

| 54       | P12/SEG36      | K12      | I   | _           | Key matrix input                                    |

| 55       | P11/SEG35      | K13      | 1   |             |                                                     |

| 56       | P10/SEG34      | K14      | 1   |             |                                                     |

| 57       | P07/SEG33      | SFT      | 0   | _           | VCO frequency range change                          |

| 58       | P06/SEG32      | SD       | 0   | Active low  | Signal detection output                             |

| 59       | P05/SEG31      | AFC      | 0   | Active high | AF tone control output                              |

| 60       | P04/SEG30      | DA4      | 0   |             |                                                     |

| 61       | P03/SEG29      | DA3      | 0   | _           |                                                     |

| 62       | P02/SEG28      | DA2      | 0   | _           | DA converter for electronic volume and output power |

| 63       | P01/SEG27      | DA1      | 0   |             |                                                     |

| 64       | P00/SEG26      | DAO      | 0   |             |                                                     |

| 65       | P37/SEG25      | S25      | 0   | _           |                                                     |

| 66       | P36/SEG24      | S24      | 0   |             |                                                     |

| 67       | P35/SEG23      | S23      | 0   |             |                                                     |

| 68       | P34/SEG22      | S22      | 0   |             |                                                     |

| 69       | P33/SEG21      | S21      | 0   | _           |                                                     |

| 70       | P32/SEG20      | S20      | 0   | <br>_       |                                                     |

| 71       | P31/SEG19      | S19      | 0   |             |                                                     |

| 72       | P30/SEG18      | S18      | 0   |             |                                                     |

| 72       | SEG17          | S17      | 0   |             |                                                     |

| 73       | SEG16          | S16      | 0   |             |                                                     |

| 74       | SEG15          | S15      | 0   |             |                                                     |

| 76       | SEG14          | S13      | 0   |             |                                                     |

| 70       | SEG13          | S14      | 0   | _           |                                                     |

| 78       | SEG12          | S12      | 0   |             | LCD segment signal                                  |

| 78       | SEG12<br>SEG11 | S12      | 0   |             |                                                     |

| 80       | SEG10          | S10      | 0   |             |                                                     |

| 81       | SEG9           | S10      | 0   |             | 4                                                   |

| 82       | SEG8           | S8       | 0   | -           |                                                     |

| o∠<br>83 | SEG7           | 50<br>S7 | 0   |             |                                                     |

| 84       | SEG7           | 57<br>S6 | 0   |             | 4                                                   |

| 85       | SEG6<br>SEG5   | 50<br>S5 | 0   |             | 4                                                   |

| 86       | SEG5<br>SEG4   | 55<br>S4 | 0   | -           |                                                     |

| 87       | SEG4           | 54<br>S3 | 0   |             |                                                     |

|          | SEG3           | 53<br>S2 | 0   | -           |                                                     |

| 88       | SEG2           | 52<br>S1 | 0   |             |                                                     |

| 89       |                |          | 0   | -           | 4                                                   |

| 90       | SEG0           | S0       |     |             | CPU power torminal                                  |

| 91       | VCC            | VDD      | -   | -           | CPU power terminal                                  |

| 92       | VREF           | AVSS     |     | -           | AD converter power supply                           |

| 93       | AVSS<br>COM3   |          | -   | -           | AD converter ground                                 |

| 94       |                | COM3     |     |             |                                                     |

| 95       | COM2           | COM2     | 0   | -           | LCD COM2 output                                     |

| 96       |                | COM1     | 0   | -           |                                                     |

| 97       | COMO           | COMO     | 0   | r <b>-</b>  |                                                     |

| 98       | VL3            | VL3      |     | -           | LCD power supply                                    |

| 99       | VL2            | VL2      |     | -           | LCD power supply                                    |

| 100      | C2             | I        | -   | -           | -                                                   |

### ADJUSTMENT

### 1) Required Test Equipment

The following items are required to adjust radio parameters:

- 1. Regulated power supply

- 2. Digital multimeter

- 3. Oscilloscope

- 4. Audio dummy load

- 5. SSG

- 6. Spectrum Analyzer

- 7. Power meter

- 8. Audio volmeter

- 9. Audio generator

- 10. Distortion meter /SINAD meter

- 11. Frequency counter

- 12. Linear detector

### Note

- Standard modulation:

- Reference sensitivity:

- $\blacksquare$  Specified audio output level: 200 mW at 8  $\Omega$

- $\blacksquare$  Standard audio output level: 50 mW at 8  $\Omega$

- Use an RF cable (3D2W: 1 m) for test equipment.

- Attach a fuse to the RF test equipment.

- All SSG outputs are indicated by EMF.

- Supply voltage for the transceiver: 13.8 VDC

Supply voltage: Current:

Voltage range: Current: Input resistance:

Measurable frequency:

Impedance: Dissipation: Jack:

Output frequency: Output level: Modulation:

Measuring range:

Measurable frequency: Impedance: Measuring range:

Measurable frequency: Sensitivity:

Output frequency: Output impedance:

Measurable frequency: Input level: Distortion level:

Measurable frequency: Measurable stability:

Measurable frequency: Characteristics: CN:

1 kHz +/-3.5 kHz/DEV

12 dB SINAD

5 - 14 VDC 3 A or more

FS = Approx. 20 V 10A or more High impedance

Audio frequency

8 Ω 1 W or more 3.5 mm φ

200 MHz or more -20 dB/0.1 μ V - 120dB/1V AM/FM

Up to 2 GHz or more

Up to 200 MHz 50  $\Omega$  , unbalanced 0.1 W - 10 W

Up to 100 kHz 1 mV to 10 V

67 Hz to 10 kHz 600  $\Omega$  , unbalanced

1 kHz Up to 40 dB 1 % - 100 %

Up to 200 MHz Approx. +/-0.1 ppm

Up to 200 MHz Flat 60 dB or more

### 2) Adjustment Mode

The DJ - 191 does not require a serviceperson to manipulate the components on the printed - circuit board, except the trimmer when adjusting reference frequency and deviation. Most of the adjustments for the transceiver are made by using the keys on it while the unit is in the adjustment mode. Because the adjustment mode temporarily uses the channels, frequency must be set on each channel before adjustments can be made. For instructions on how to program the channels, see the "DJ - 191 INSTRUCTION MANUAL" which came with the product. In consideration of the radio environment, the frequency on each channel must be near the value (+/ - 1 MHz) listed in the table below. To enter the adjustment mode, turn the power off, hold down both the UP and DOWN keys, and press the POWER key. "chEc" appears on the LCD for about two seconds, and "C" appears indicating the unit is in the adjustment mode.

#### Channel **Channel function** Frequency 1 Reference frequency adjustment 145 MHz 2 High power adjustment 145 MHz 3 145 MHz Low power adjustment 4 Minimum frequency sensitivity adjustment 130 MHz 5 Medium frequency sensitivity adjustment 145 MHz 6 Maximum frequency sensitivity adjustment 173 MHz 7 S-meter (1) adjustment 145 MHz 8 S-meter (FULL) adjustment 145 MHz 9 Deviation 145 MHz 145 MHz 10 DTMF (1) test 11 DTMF (D) test 145 MHz 145 MHz 12 Tone 67 Hz test Tone 88.5 Hz test 145 MHz 13 Tone 250.3 Hz test 145 MHz 14 Tone burst test 145 MHz 15 Aging (Not required to use) 145 MHz 16 20 VCO frequency shift change (Do not change).

#### Channel frequencies used in the adjustment mode

#### Caution

■ Do not press the UP or DOWN key while channel 20 is selected in the adjustment mode. Otherwise, the VCO switch frequency will change, causing a malfunction.

### Reference Frequency Adjustment

- 1. In the adjustment mode, select channel 1 by rotating the main tuning dial.

- 2. Press the (PTT,) key to start transmission.

- 3. Rotate TC101 on the RF circuit board until the value on the frequency counter matches the one displayed on the LCD.

### High Power Adjustment

- 1. In the adjustment mode, select channel 2 by rotating the main tuning dial.

- 2. Hold down the F key and press the H/L key to enter the high power mode ("L" at the lower-left of the display disappears).

- 3. Hold down the (PTT) key to start transmission.

- 4. While watching the reading of the TX power meter, set the output power to the value closest to 5 W by using the UP and DOWN keys.

- 5. When the PTT key is released, the output power at that time will be stored as the high power setting.

### Low Power Adjustment

- 1. In the adjustment mode, select channel 3 by rotating the main tuning dial.

- 2. Hold down the (F) key and press the (H/L) key to enter the low power mode ("L" appears at the lower-left of the display).

- 3. Hold down the (PTT) key to start transmission.

- 4. While watching the reading of the TX power meter, set the output power to the value closest to 0.5 W by using the UP and OOWN keys.

- 5. When the PTT key is released, the output power at that time will be stored as the low power setting.

### Minimum Frequency Sensitivity Adjustment

See "Note on Adjusting the Sensitivity" later in this section.

- 1. In the adjustment mode, select channel 4 by rotating the main tuning dial.

- 2. Using the UP and DOWN key, set the minimum frequency sensitivity.

### Medium Frequency Sensitivity Adjustment

- See "Note on Adjusting the Sensitivity" later in this section.

- 1. In the adjustment mode, select channel 5 by rotating the main tuning dial.

- 2. Using the <u>UP</u> and <u>DOWN</u> key, set the medium frequency sensitivity.

### Maximum Frequency Sensitivity Adjustment

- See "Note on Adjusting the Sensitivity" later in this section.

- 1. In the adjustment mode, select channel 6 by rotating the main tuning dial.

- 2. Using the UP and DOWN key, set the maximum frequency sensitivity.

| S-meter (1) Adjustment       | <ol> <li>In the adjustment mode, select channel 7 by rotating the main tuning dial. The S-meter will show a single star (★).</li> <li>Enter "0" dB μ (EMF) with the transceiver tester.</li> <li>Press the DOWN key. The transceiver beeps indicating the new setting has been stored successfully.</li> </ol>                                                                                     |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S-meter (FULL)<br>Adjustment | <ol> <li>In the adjustment mode, select channel 8 by rotating the main tuning dial. The S-meter will show all six stars (★ ★ ★ ★ ★ ★).</li> <li>Enter "+20" dB μ (EMF) with the transceiver tester.</li> <li>Press the DOWN key. The transceiver beeps indicating the new setting has been stored successfully.</li> </ol>                                                                         |

| Deviation                    | <ol> <li>In the adjustment mode, select channel 9 by rotating the main tuning dial.</li> <li>Input a 50 mVrms, 1 KMz signal with your transceiver tester through the external microphone jack.</li> <li>With the tester, put the transceiver in the transmission mode.</li> <li>Rotate the VR2 on the printed - circuit board of the transceiver until the deviation is set to 4.5 KHz.</li> </ol> |

| DTMF (1) Test                | <ol> <li>This function is only for checking the DTMF code, not adjusting it.</li> <li>In the adjustment mode, select channel 10 by rotating the main tuning dial.</li> <li>Press the PTT key. DTMF code "1" is automatically sent and you will hear the monitoring tone from the speaker.</li> <li>Check the deviation with the transceiver tester.</li> </ol>                                     |

| DTMF (D) Test                | <ol> <li>In the adjustment mode, select channel 11 by rotating the main tuning dial.</li> <li>Press the PTT key. DTMF code "D" is automatically sent and you will hear the monitoring tone from the speaker.</li> <li>Check the deviation with the transceiver tester.</li> </ol>                                                                                                                  |

| Tone 67 Hz Test              | <ol> <li>This function is only for checking the tone encoder, not adjusting it.</li> <li>In the adjustment mode, select channel 12 by rotating the main tuning dial.</li> <li>Press the PTT key. A 67 Hz tone is automatically sent.</li> <li>Check the deviation with the transceiver tester.</li> </ol>                                                                                          |

| Tone 88.5 Hz Test            | <ol> <li>In the adjustment mode, select channel 13 by rotating the main tuning dial.</li> <li>Press the PTT key. An 88.5 Hz tone is automatically sent.</li> <li>Check the deviation with the transceiver tester.</li> </ol>                                                                                                                                                                       |

### Tone 250.3 Hz Test

- 1. In the adjustment mode, select channel 14 by rotating the main tuning dial.

- 2. Press the (PTT) key. A 250.3 Hz tone is automatically sent.

- 3. Check the deviation with the transceiver tester.

### **Tone Burst Test**

This function is only for checking the tone burst, not adjusting it.

- 1. In the adjustment mode, select channel 15 by rotating the main tuning dial.

- 2. Press the PTT key. A 1750 Hz tone burst is automatically sent.

- 3. Check the deviation with the transceiver tester.

Perform this aging test only when necessary.

1. In the adjustment mode, select channel 16 by rotating the main tuning dial. The transceiver automatically repeats transmission for a minute and reception for another minute.

Note on Adjusting Sensitivity

Sensitivity is adjusted by applying the optimum voltage from the CPU to the varicap of the tuning circuit. The coil manipulation for L109, L110, L111, and L112 is not required. If any of the coils is accidentally rotated, return it to the default position as described below, before adjusting the sensitivity.

- 1. Program any frequency within 145 MHz +/-1 on memory channel 5.

- 2. Holding down both the UP and DOWN key, press the POWER switch to turn the power ON. "chEc" will appears on the LCD for two seconds, and "C" appears.

- 3. Select channel 5 by rotating the main tuning dial.

- 4. Using the UP and DOWN keys, set the adjustment data to "7F" ("7F" appears in the channel number area on the LCD).

- 5. Turn the power OFF.

- 6. Holding down both the UP and DOWN key, turn the power ON. When the "C" no longer appears, the transceiver is in the normal status.

- 7. Set the reception frequency to 145 MHz +/-1. Rotate the coil to maximize the sensitivity.

Aging

# CIRCUIT DIAGRAM

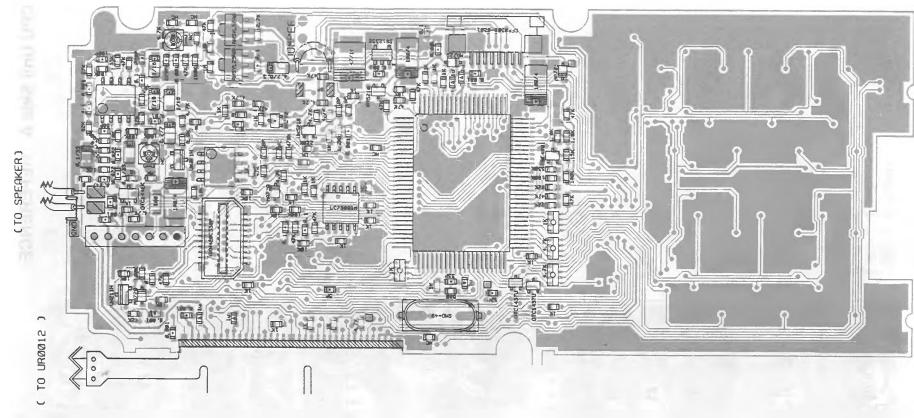

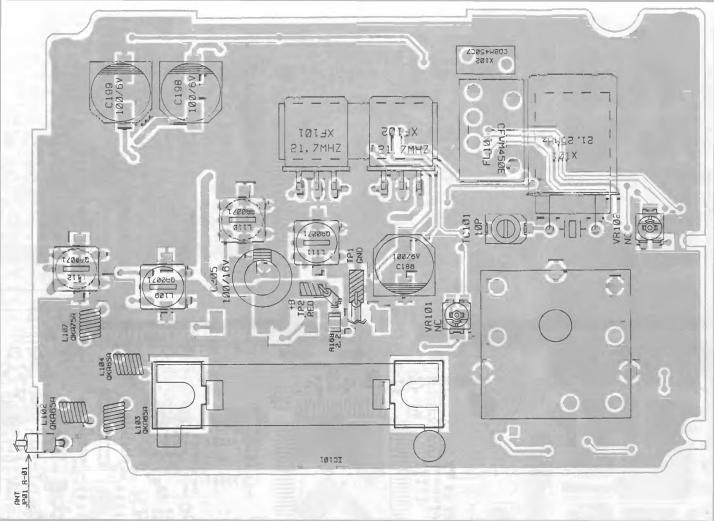

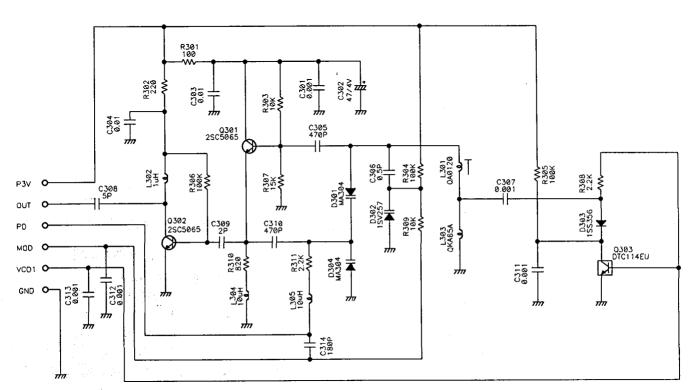

**VCO UNIT**

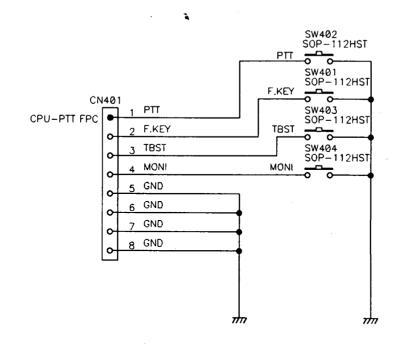

**SW UNIT**

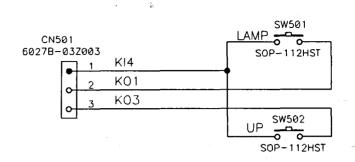

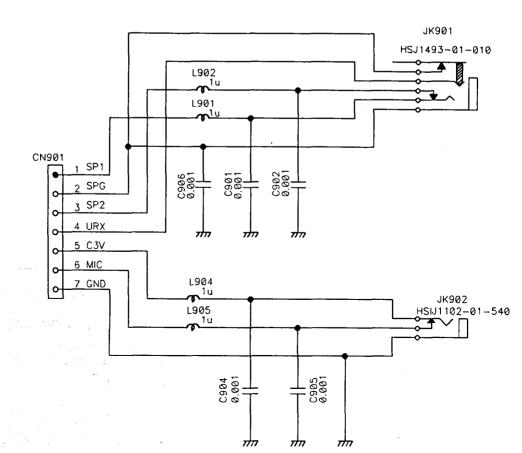

### **SP-JACK UNIT**

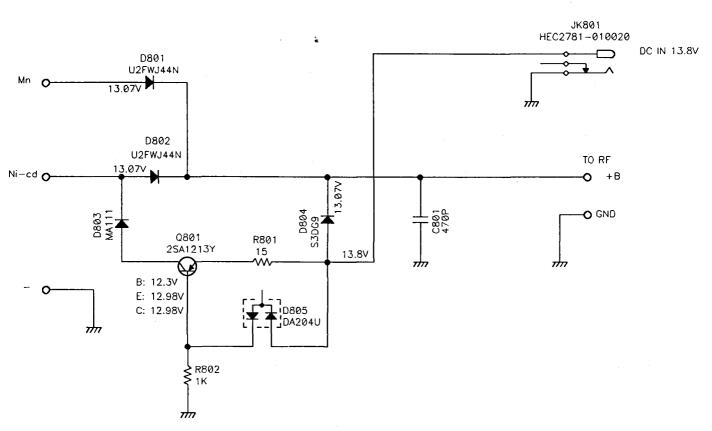

### **CHARGE UNIT**

1

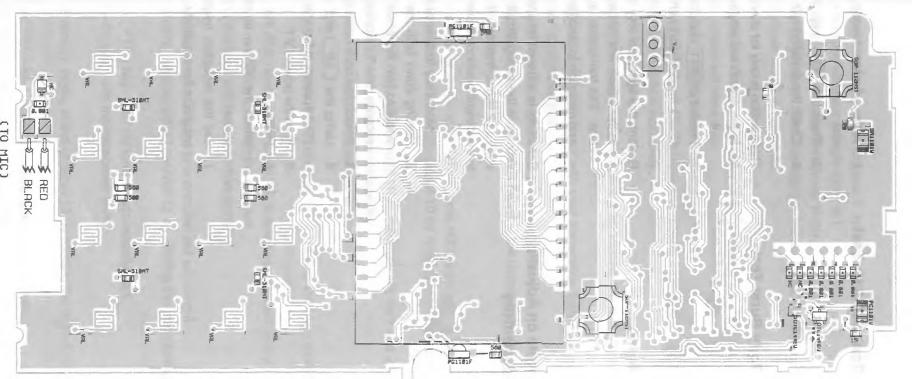

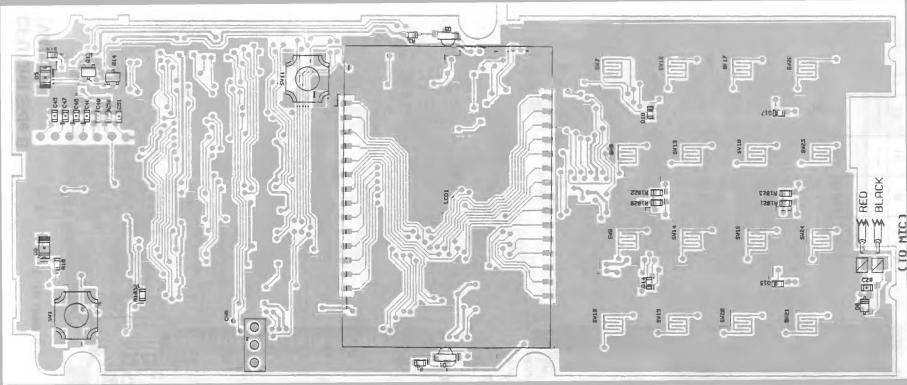

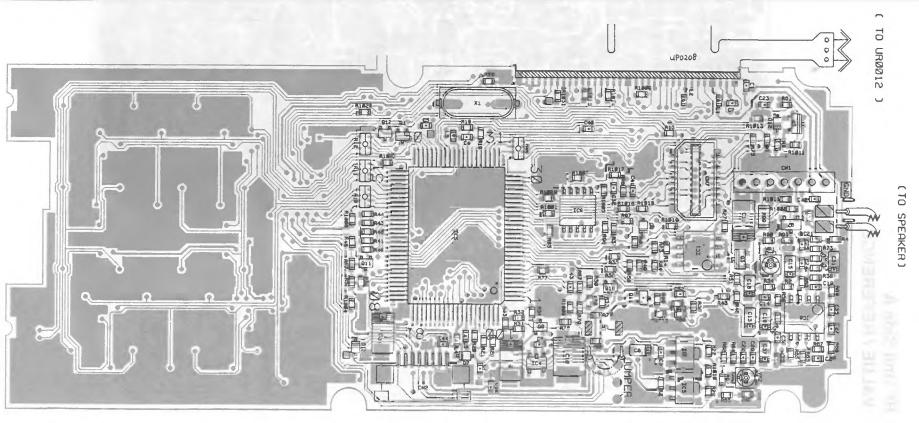

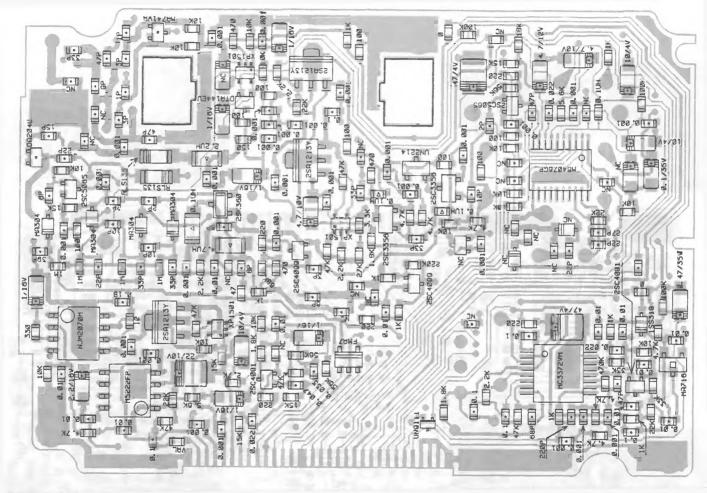

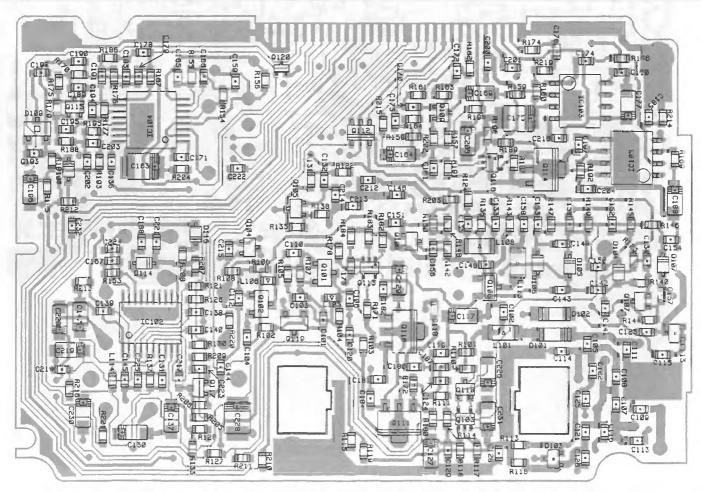

**RF UNIT**

+B

0-